T2R2 東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

### 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Low-Power and Small-Area RF Transceiver Front-End with Direct<br>Antenna Interface                                                                                                           |

| 著者(和文)            | Sun Zheng                                                                                                                                                                                    |

| Author(English)   | Zheng Sun                                                                                                                                                                                    |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12005号,<br>授与年月日:2021年3月26日,<br>学位の種別:課程博士,<br>審査員:岡田 健一,髙木 茂孝,廣川 二郎,德田 崇,伊藤 浩之,飯塚 哲也                                                                 |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12005号,<br>Conferred date:2021/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                         |

| Type(English)     | Doctoral Thesis                                                                                                                                                                              |

## Low-Power and Small-Area RF Transceiver Front-End with Direct Antenna Interface

by

Zheng Sun

A Ph. D. dissertation submitted in partial satisfaction of the requirements for the degree of

### **Doctor of Philosophy**

in

### **Department of Physical Electronics**

in the

### **Graduate School of Science and Engineering**

of

### **Tokyo Institute of Technology**

Supervised by

Prof. Kenichi Okada

Spring 2021

To my family,

### Acknowledgment

This thesis stands on years of hard work and the generous help that I have experienced and received over the five years of the Ph.D. study. Thus, I would first like to take this chance to acknowledge the people who have helped and encouraged me throughout my entire five+ year's doctor course in the Tokyo Institute of Technology. Also I want to acknowledge the organization which supports our research during the five years.

First and foremost, I would like to express my gratitude to my supervisor Professor Kenichi Okada for giving me a wonderful chance to study in this top-level IC design laboratory. From 2015, I became a doctoral student in this lab, and I cannot adhere to now without his valuable advice and kindly help in both research and life in Japan. During these years, he squeezed enough time from his tight daily schedule and guided us in both research and life. Without the discussions and his guidance, many ideas cannot be generated. Also, these ideas cannot be realized without his trust and support. With no doubt, this thesis also could not be finished without his continuous guidance and support throughout the five years.

I would also like to thank Professor Akira Matsuzawa for his kindly teaching and guidance when I first came to this laboratory. Even now I still remember he taught me how to do the presentation in front of many people. What he taught me benefits me a lot, not just limited to research also including the lifestyle and attitude. I also want to thank for his kindly inviting to his house and have a big party with everyone, which enrich my life outside the laboratory and gave me many unforgettable moments in Japan. By talking with him, many genius thoughts are shared with each other, which broaden my vision. Professor Masaya Miyahara is also so kind to give our suggestions and advice when I got into problems. And I also want to thank him for his generous help and practical help.

During the five years, a lot of help are given by the secretaries in this laboratory, Yoshino Kasuga, Makiko Tsunashima and Ayumi Okubo. Because they deal with complicated paper works, I can have more time to focus on the research. It was their help that made everything go smoothly. Their advice, explanations and reminders are always helpful in the study and life.

I would also like to show my gratitude to the Ph.D. committee members, Prof. Shige-

taka Takagi, Prof. Jiro Hirokawa, Prof. Takashi Tokuda, Prof. Hiroyuki Ito, and Prof. Tetsuya Iizuka for taking the time out of their busy schedule to examine my dissertation and attend my final presentation. Thank them for their valuable advice and suggestions, and this work becomes more meaningful and inspired.

Here, I would like to express my gratitude to my seniors, Hanli Liu, Jian Pang, Bangan Liu, Rui Wu, Aravind Tharayil Narayanan and Tohru Kaneko for all their kind help and rich knowledge that they have shared with me. Without their valuable advice, it is impossible to reach the current result. Also, I want to thank them for sharing precious time and happy things with me, which greatly enrich my life in Japan.

Also, I would like to thank the BLE group members: Dexian Tang, Hongye Huang, and Dingxin Xu. Without their help and effort, this work can not be finished, and thank them for sharing knowledge and happiness in life. I also thanks to them for staying with me in a difficult time and hope they all have a bright future. I also want to thank the PLL group members. It was the discussion and knowledge shared by them that turned many ideas into reality.

Finally, I want give my most sincere thanks to my girlfriend, Dan Qiao, for sharing the wonderful life with me in Japan. Thank her for accompanying me to Japan and start a new life here. Also, thank her for encouraging me in a hard time and appropriate her for her effort in pursuing a better life. It was her devotion that allowed me to achieve my current result, and she is the motivation that keeps me going. I would also like to express gratitude to my parents for supporting me in studying overseas and for their kindly concern.

### Abstract

This thesis presents low-power and small-area Bluetooth Low-Energy transceiver for short-range internet-of-things applications. To realize small size and long life-time modules, architecture considerations and key building blocks are discussed. An integrated radio-frequency input-output embedded with transmitter/receiver switch function and onchip impedance matching is proposed. The proposed radio-frequency input-output is designed with minimized noise factor penalty for high-sensitivity receiver operation and harmonic suppression function for satisfying the out-of-band spurious emission requirements. To lower the power consumption and mitigate the supply variation with small on-chip area, a transformer-based low-power voltage-controlled oscillator with supply pushing reduction is presented and discussed in this thesis.

# Contents

| Ac | cknov  | vledgme | ent                                                           | iii |

|----|--------|---------|---------------------------------------------------------------|-----|

| Ał | ostrac | :t      |                                                               | v   |

| 1  | Intr   | oductio | n                                                             | 1   |

|    | 1.1    | Interne | et-of-Things and its Available Wireless Standards             | 1   |

|    |        | 1.1.1   | Medium-Range and Long-Range Wireless Standard                 | 3   |

|    |        | 1.1.2   | Short-Range Wireless Standard                                 | 4   |

|    | 1.2    | Blueto  | oth Transceiver and its Applications                          | 5   |

|    | 1.3    | Challe  | nges for RF Front-End Design with Direct Antenna Interface    | 10  |

|    |        | 1.3.1   | General Challenges for BLE TRXs                               | 10  |

|    |        | 1.3.2   | Academic Challenges                                           | 11  |

|    |        | 1.3.3   | Fundamental Issues                                            | 12  |

|    |        | 1.3.4   | Specification Consideration                                   | 12  |

|    | 1.4    | Long I  | Life-Time and Easy Implementation                             | 25  |

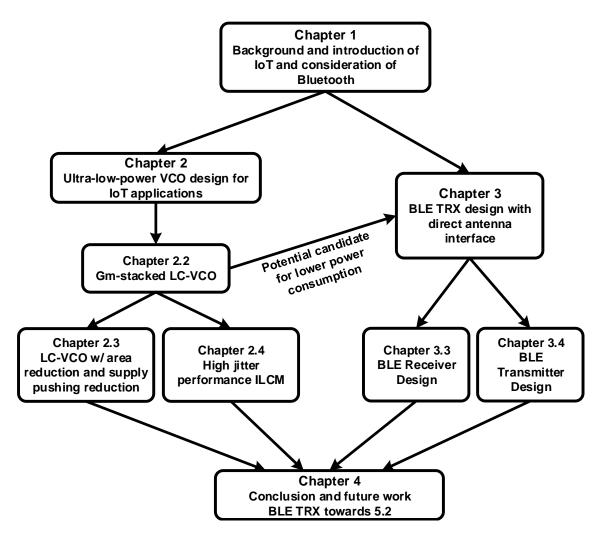

|    | 1.5    | Overvi  | iew of the Thesis                                             | 29  |

| 2  | Ultr   | a-Low-  | Power Transformer-based LC-VCO                                | 35  |

|    | 2.1    | Low-P   | Power LC-VCO and Implementation in PLL Design                 | 35  |

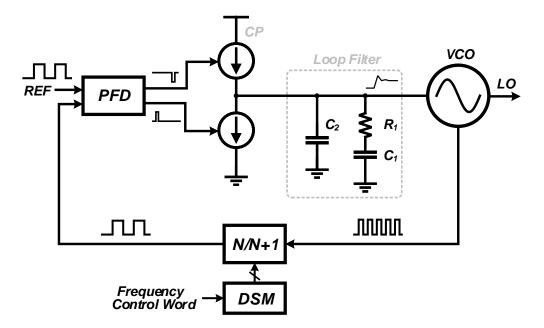

|    |        | 2.1.1   | LC-VCO in Conventional PLL Design                             | 36  |

|    |        | 2.1.2   | Phase Noise in LC-VCO                                         | 45  |

|    | 2.2    | Propos  | sed Gm-Stacked VCO using Transformer                          | 50  |

|    | 2.3    | Desigr  | Procedures of Transformer-Based VCO                           | 57  |

|    | 2.4    | Area-F  | Reduction and Supply Pushing Reduction                        | 58  |

|    |        | 2.4.1   | Transformer with Patterned Ground Shields                     | 60  |

|    |        | 2.4.2   | Supply Pushing Reduction                                      | 65  |

|    | 2.5    | Measu   | rement Results of The ULP VCO with Supply Pushing Reduction . | 75  |

|    | 2.6    | A Higl  | h Jitter Performance Injection-Locked Clock Multiplier        | 77  |

|    |        | 2.6.1   | Transformer-Based ULP VCO                                     | 83  |

|   |      | 2.6.2     | Transformer-Based Tank and Start-up Condition                |

|---|------|-----------|--------------------------------------------------------------|

|   |      | 2.6.3     | Low flicker Noise Corner                                     |

|   |      | 2.6.4     | ILCM Implementation                                          |

|   |      | 2.6.5     | Measurement Results of ILCM                                  |

|   | 2.7  | Conclu    | sion of ILCM 97                                              |

| 3 | Blue | etooth L  | ow Energy Transceiver with Direct Antenna Interface 99       |

|   | 3.1  |           | ew of BLE Transceiver Design                                 |

|   | 3.2  |           | Frequency Input-Output                                       |

|   |      | 3.2.1     | RFIO                                                         |

|   |      | 3.2.2     | LNA and G <sub>m</sub>                                       |

|   |      | 3.2.3     | PA                                                           |

|   |      | 3.2.4     | Transformer                                                  |

|   | 3.3  | High D    | ynamic-Range Low-Power Receiver                              |

|   |      | 3.3.1     | BLE Receiver in High/Mid Gain Mode                           |

|   |      | 3.3.2     | BLE Receiver in LNA Bypass Mode                              |

|   | 3.4  | High E    | fficiency and Harmonic-Suppressed Transmitter                |

|   |      | 3.4.1     | HD2 Rejection                                                |

|   |      | 3.4.2     | HD3 Suppression                                              |

|   | 3.5  | Measur    | rement Results                                               |

|   | 3.6  | Conclu    | sion                                                         |

| 4 | Con  | clusion a | and Future Works 145                                         |

|   | 4.1  | Conclu    | sion of the Thesis                                           |

|   | 4.2  | Contrib   | pution of the Thesis                                         |

|   | 4.3  | Bluetoo   | oth Transceiver Towards 5.2                                  |

|   | 4.4  | Small-    | Area and Low-Power TX using A Sub-200 µW Ring-Oscillator 149 |

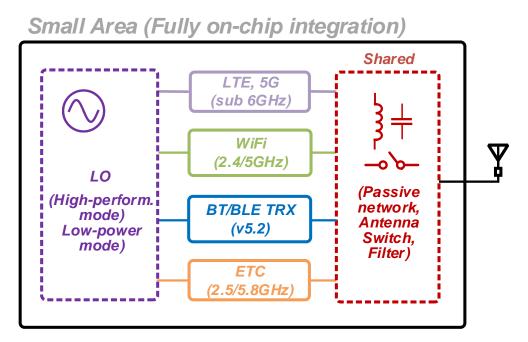

|   | 4.5  | BT 5.2    | TRX with Multiple Power Mode                                 |

| A | Pub  | lication  | List 173                                                     |

|   | A.1  | Journal   | Papers                                                       |

|   | A.2  |           | tional Conferences                                           |

|   | A.3  | Domes     | tic Conferences                                              |

|   | A.4  | Co-Aut    | thor                                                         |

|   |      | A.4.1     | Journal Papers                                               |

|   |      | A.4.2     | International Conferences                                    |

|   |      | A.4.3     | Domestic Conferences and Workshops                           |

# **List of Figures**

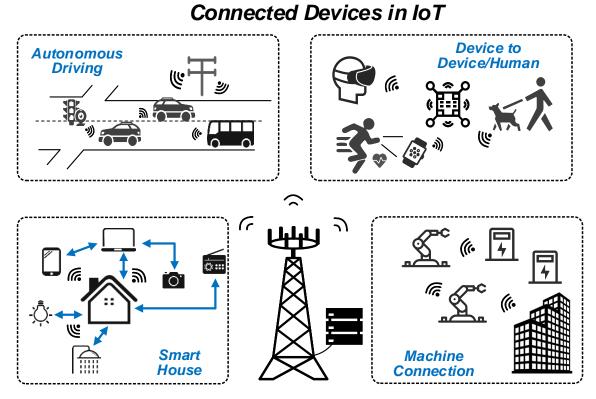

| 1.1  | The concept of the Internet of Things                                 | 2  |

|------|-----------------------------------------------------------------------|----|

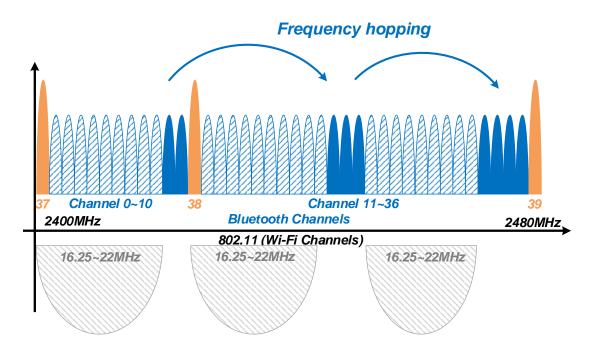

| 1.2  | The channels of Bluetooth standard and its coexistence with Wi-Fi     | 5  |

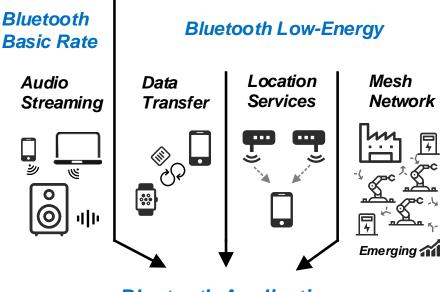

| 1.3  | The applications of Bluetooth and its classification.                 | 7  |

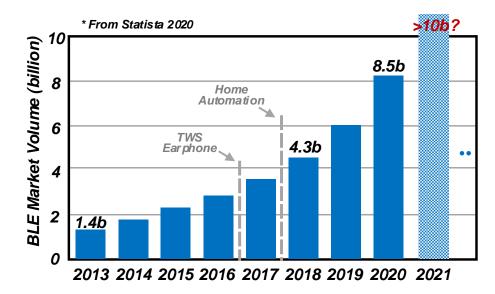

| 1.4  | The market volume of BLE applications and its trend                   | 9  |

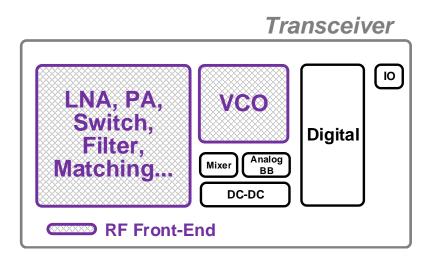

| 1.5  | The general structure for wireless transceivers                       | 11 |

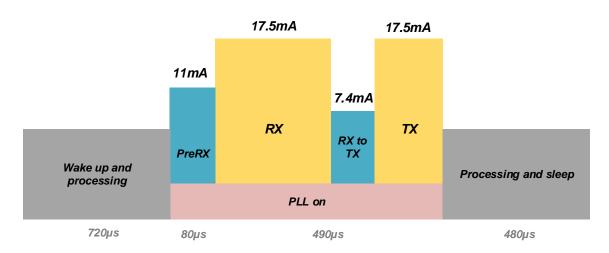

| 1.6  | Power breakdown of a Texas Instruments CC-series BLE device in a sin- |    |

|      | gle connection event.                                                 | 13 |

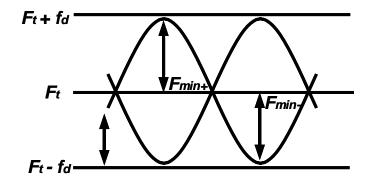

| 1.7  | The TX frequency deviation of BLE Transmitter.                        | 15 |

| 1.8  | The simplified transmitter model                                      | 16 |

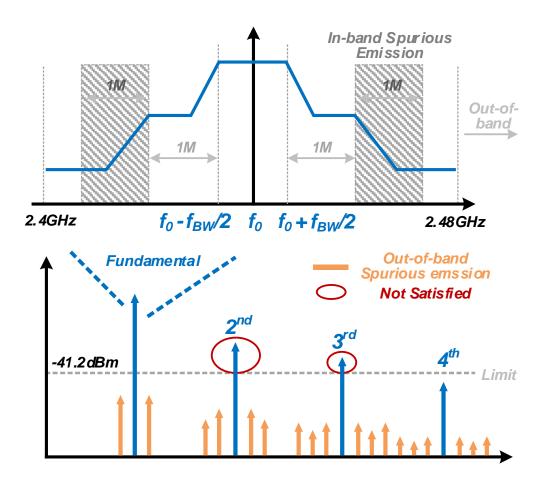

| 1.9  | The TX spurious emissions including in-band and out-of-band cases     | 17 |

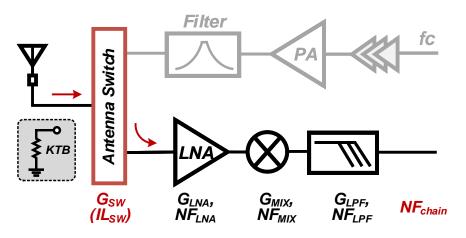

| 1.10 | The simplified receiver model.                                        | 20 |

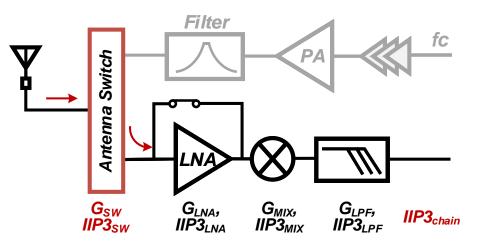

| 1.11 | The simplified receiver model for IIP3 calculation.                   | 22 |

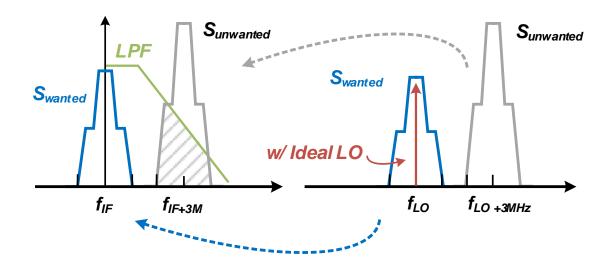

| 1.12 | The simplified receiver model for ACR calculation using ideal LO      | 23 |

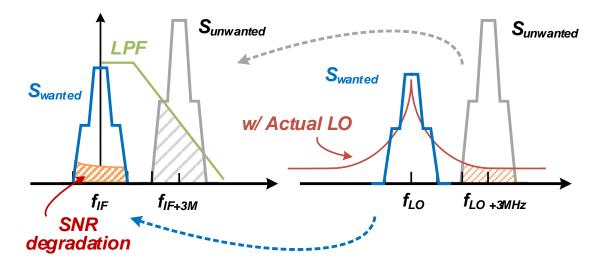

| 1.13 | The simplified receiver model for ACR calculation using actual LO     | 24 |

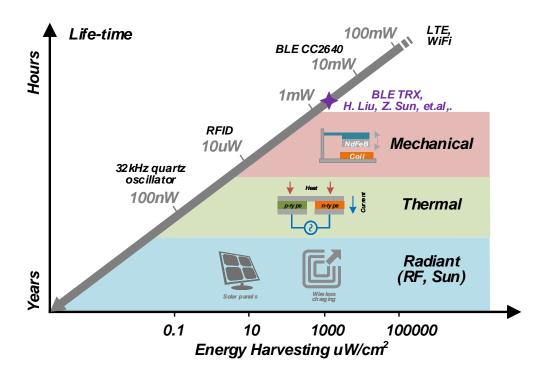

| 1.14 | Power consumption for typical applications including BLE and power    |    |

|      | densities for various energy sources.                                 | 25 |

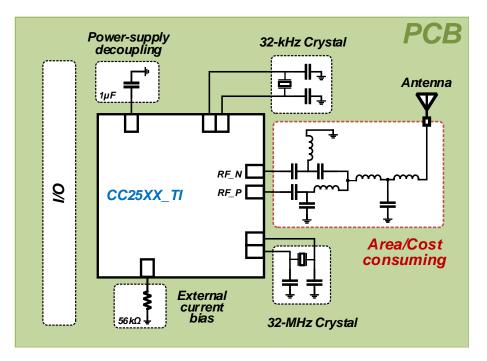

| 1.15 | A typical application circuit shown in CC-series SoC data-sheet       | 26 |

| 1.16 | Previous of BLE works.                                                | 27 |

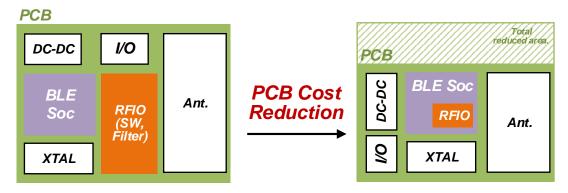

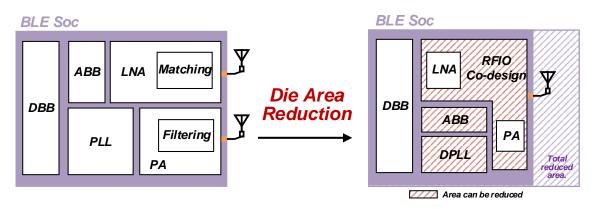

| 1.17 | The concept of PCB cost reduction for BLE applications                | 28 |

| 1.18 | The concept of SoC area reduction for BLE applications                | 29 |

| 1.19 | Measured return loss in TX and RX                                     | 32 |

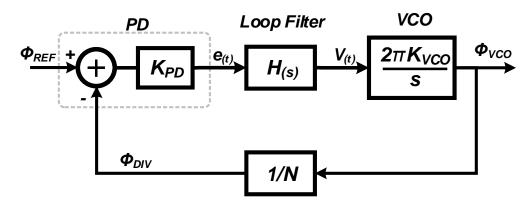

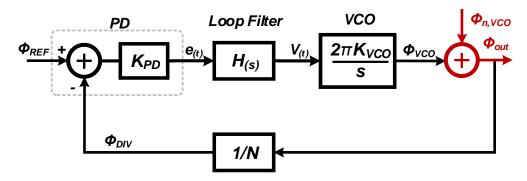

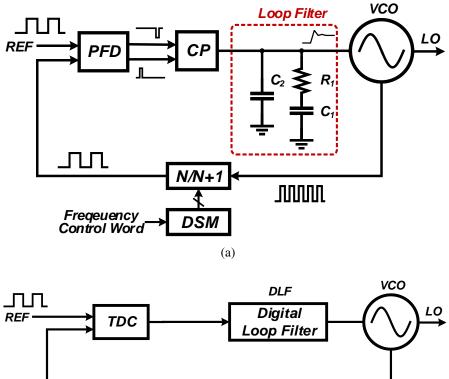

| 2.1  | Structure of the traditional charge pump based PLL                    | 36 |

| 2.2  | The frequency-domain model of the traditional charge pump based PLL   | 37 |

| 2.3  | Frequency-domain model of the VCO noise contribution in traditional   |    |

|      | charge pump based PLL.                                                | 39 |

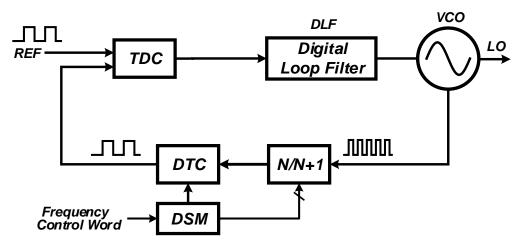

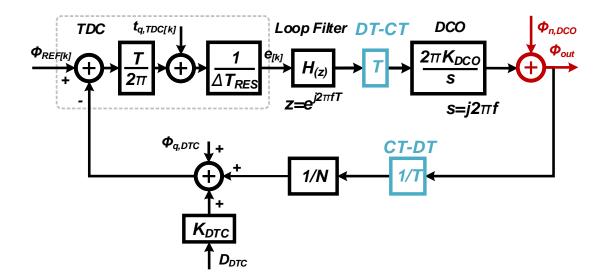

| 2.4  | Structure of the digital phase-locked loop                            | 40 |

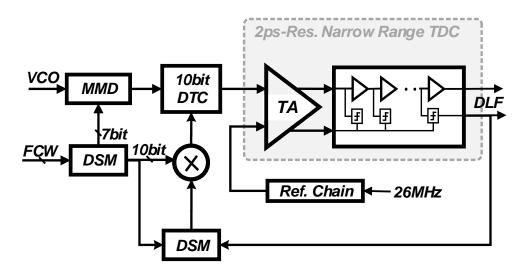

| 2.5  | The implementation of DTC and narrow-range TDC                        | 41 |

| 2.6  | Digital PLL modeling with DCO noise contribution.                     | 42 |

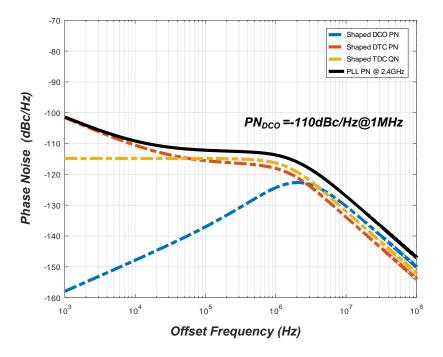

| 2.7  | DPLL noise contribution from each component ( $PN_{DCO} = -110  dBc/Hz$    |    |

|------|----------------------------------------------------------------------------|----|

|      | @1 MHz)                                                                    | 44 |

| 2.8  | DPLL noise contribution from each component ( $PN_{DCO} = -100  dBc/Hz$    |    |

|      | @1 MHz)                                                                    | 44 |

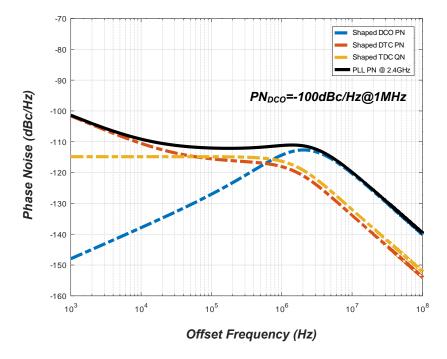

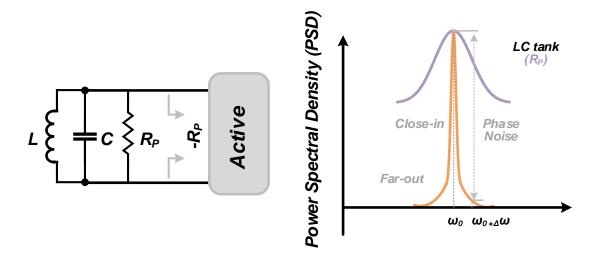

| 2.9  | LC-VCO model and its power spectral density.                               | 45 |

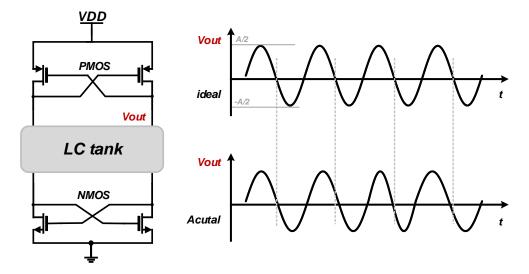

| 2.10 | Output waveform of the LC-VCO in ideal case and actual case                | 46 |

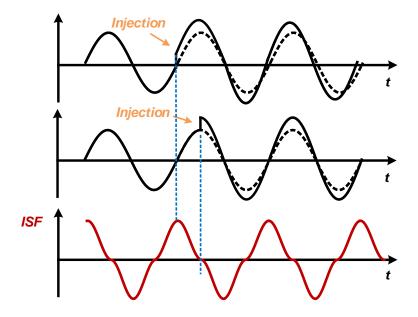

| 2.11 | Injection current at different phases in the oscillator                    | 48 |

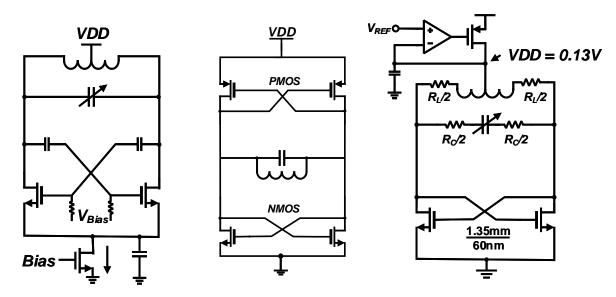

| 2.12 | Candidates for the low-power LC-VCO design.                                | 49 |

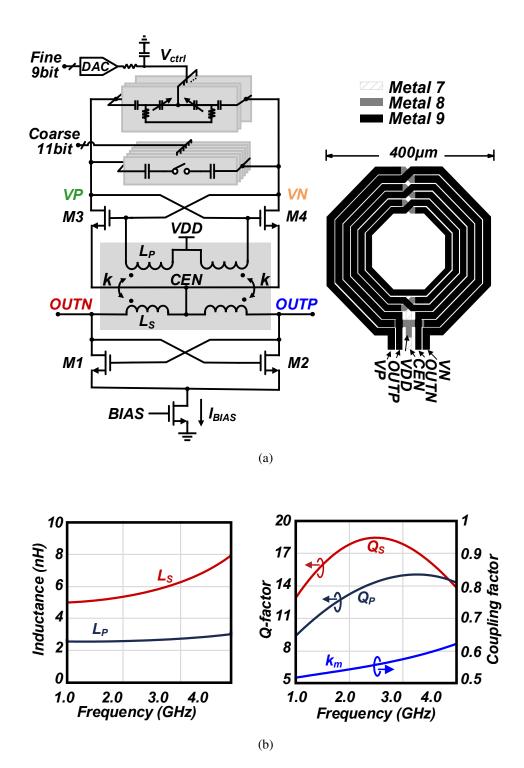

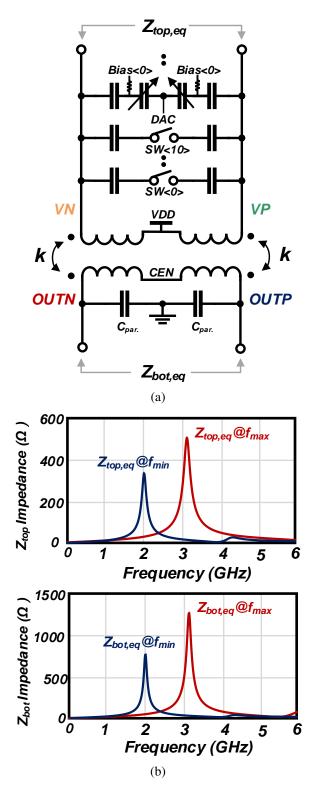

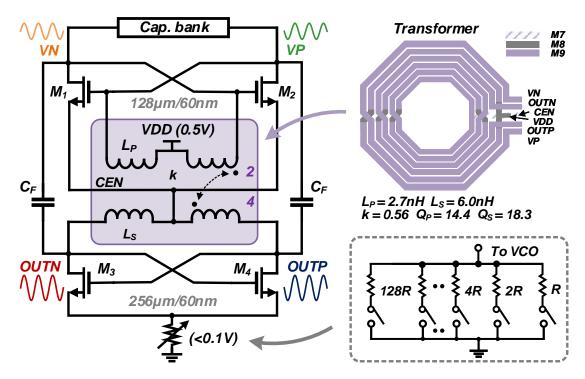

| 2.13 | (a) Proposed transformer-based stacked-gm DCO (b) Transformer with         |    |

|      | EM simulation results.                                                     | 51 |

| 2.14 | (a) Transformer with capacitor banks (b) Simulated input impedance from    |    |

|      | the top side and bot side.                                                 | 52 |

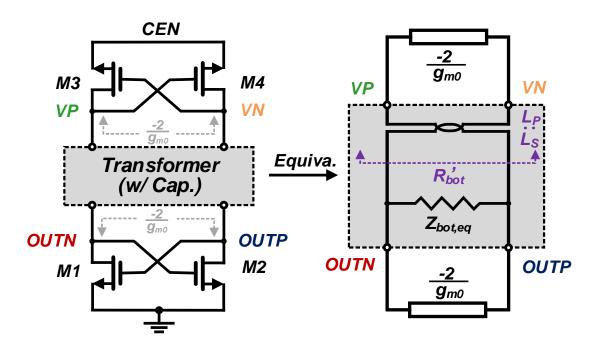

| 2.15 | Schematic redrawn of the proposed DCO and equivalent circuit               | 53 |

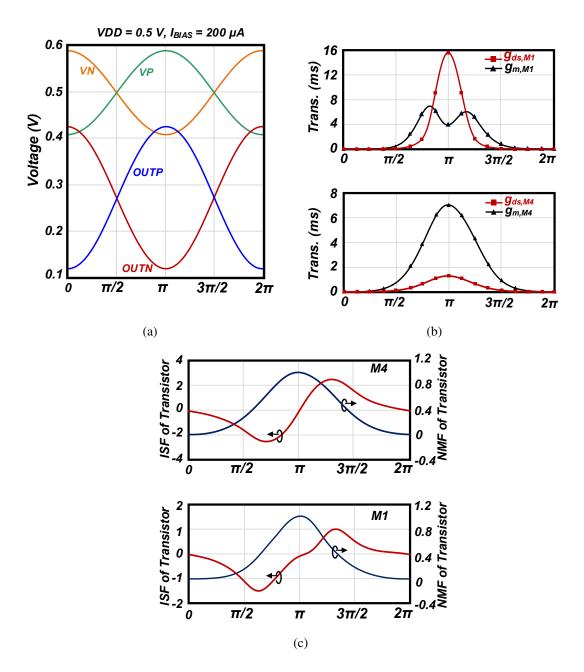

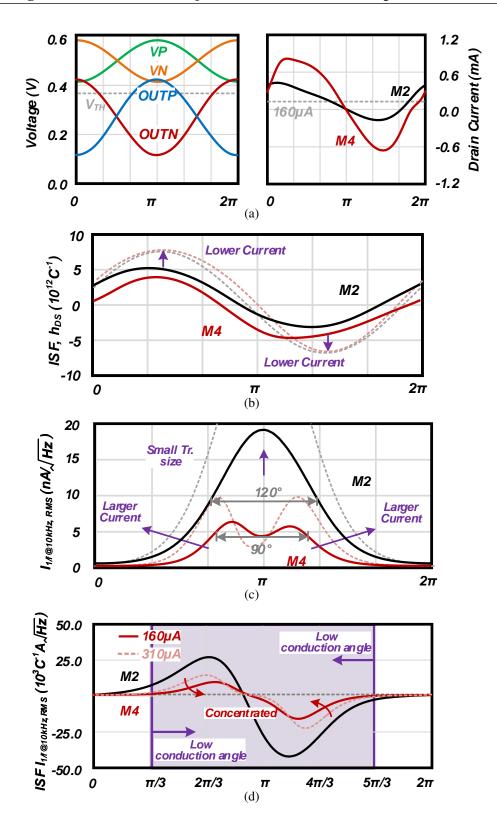

| 2.16 | (a) Simulated transient voltage waveforms of both cross-coupled pair (b)   |    |

|      | Simulated transconductance and channel conductance of M1 and M4 tran-      |    |

|      | sistors (c) Simulated ISF and NMF of the M1 and M4 transistors in the      |    |

|      | proposed DCO.                                                              | 55 |

| 2.17 | Theoretical comparison between the proposed TF-based structure and         |    |

|      | conventional structures.                                                   | 56 |

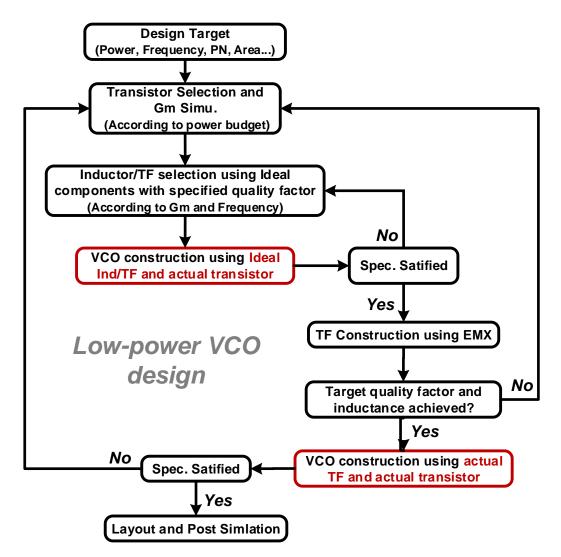

| 2.18 | Design procedures of transformer-based VCO                                 | 57 |

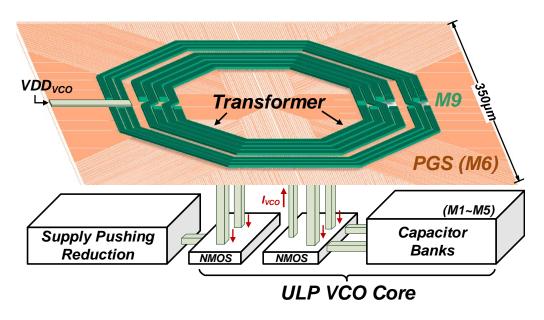

| 2.19 | ULP transformer-based VCO with minimized on-chip area and supply           |    |

|      | pushing reduction.                                                         | 59 |

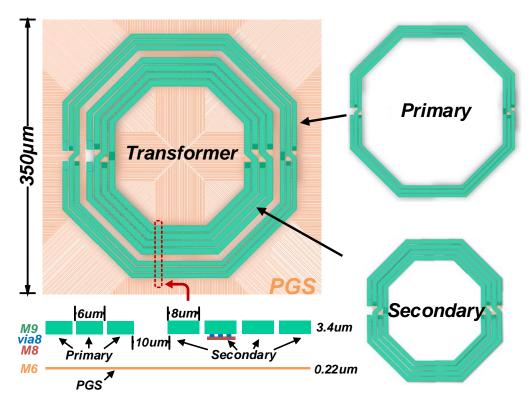

| 2.20 | Transformer with PGS.                                                      | 61 |

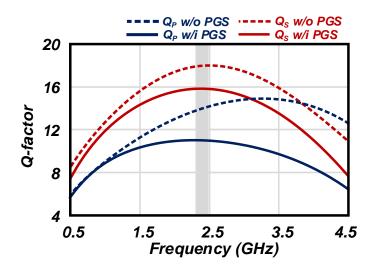

| 2.21 | EM simulation results of the transformer with and without the PGS          | 62 |

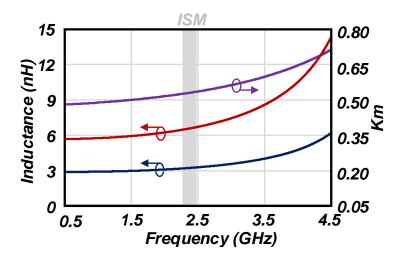

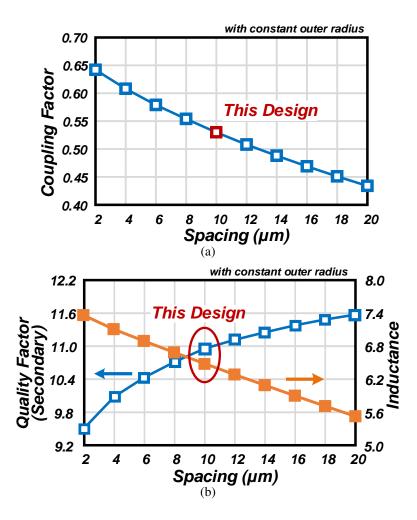

| 2.22 | EM simulation results of the transformer: inductance and coupling factor.  | 63 |

| 2.23 | EM simulation results with tuning the spacing between primary and sec-     |    |

|      | ondary windings.                                                           | 64 |

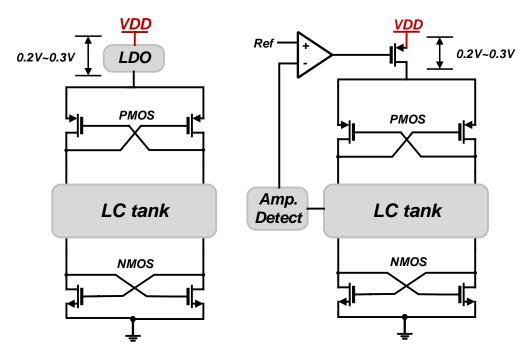

| 2.24 | Conventional CMOS structure with supply pushing reduction technique        |    |

|      | of typical LDO implementation and amplitude tracking feedback              | 66 |

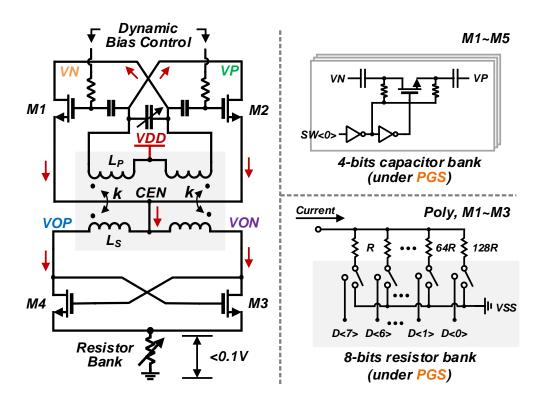

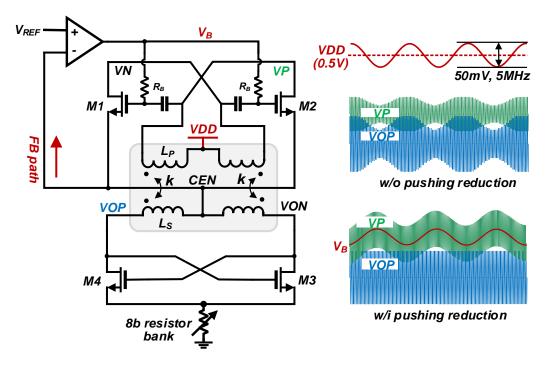

| 2.25 | TF-based LC-VCO with 4-bits capacitor banks and 8-bits resistor banks      | 67 |

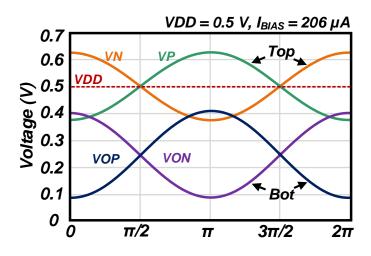

| 2.26 | Simulated waveform of each point in the proposed VCO                       | 68 |

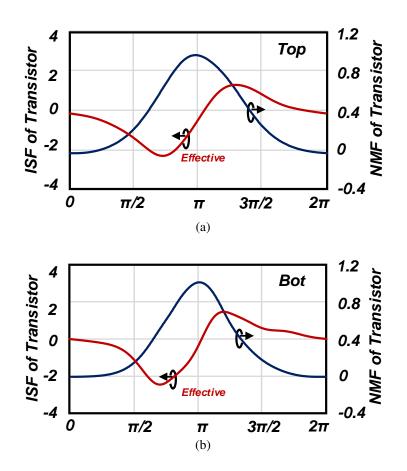

| 2.27 | Simulated ISF and NMF of transistors in the TF-based VCO: (a) top tran-    |    |

|      | sistors (b) bottom transistors.                                            | 70 |

| 2.28 | Schematic redarwn of the TF-based VCO with proposed supply pushing         |    |

|      | reduction                                                                  | 71 |

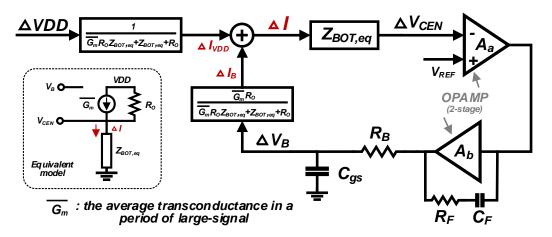

| 2.29 | Equivalent model to qualitative analyze the supply pushing reduction loop. | 72 |

#### LIST OF FIGURES

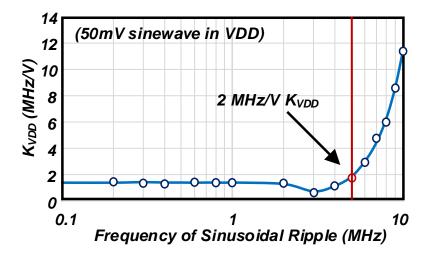

| 2.30 | Simulated supply pushing of the VCO with different sinusoidal waveform in VDD.                                                 | 73     |

|------|--------------------------------------------------------------------------------------------------------------------------------|--------|

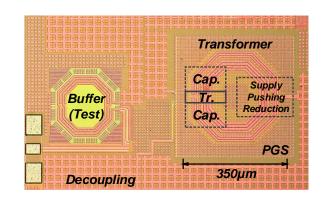

| 2.31 | Chip micrograph.                                                                                                               | 7.     |

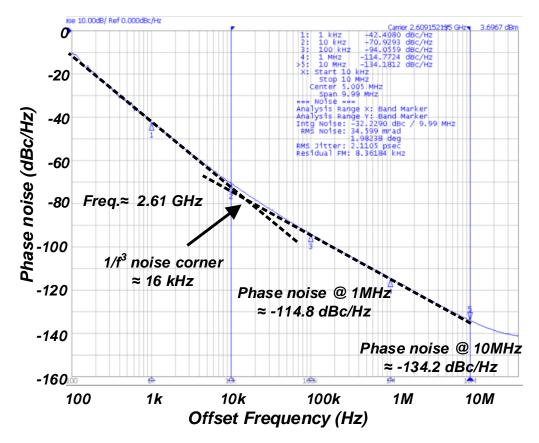

| 2.32 | Measured TF-based VCO phase noise at 2.6 GHz oscillation frequency.                                                            | 7      |

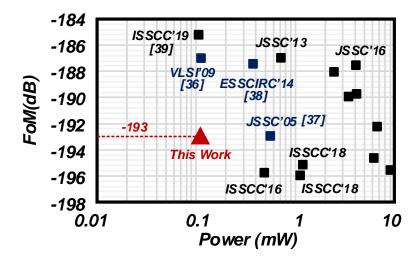

| 2.33 | The FoM summary of state-of-the-art low-power VCO designs                                                                      | 7      |

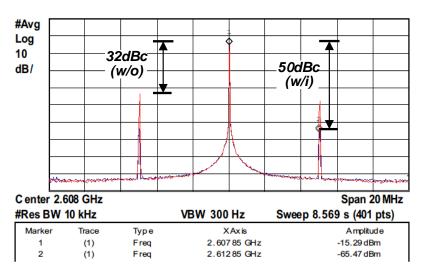

| 2.34 | Measured oscillator spectra with and without the supply pushing reduc-<br>tion under 50 mV 5 MHz sine wave.                    | 7      |

| 2.35 | Different types of phase-locked loop (a) analog type (charge-pump based)                                                       |        |

|      | (b) digital type                                                                                                               | 7      |

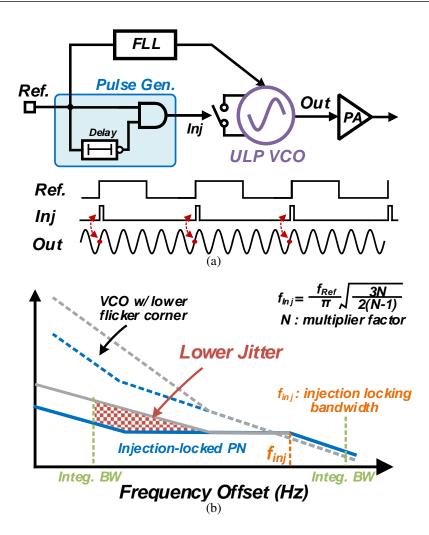

| 2.36 |                                                                                                                                | 7      |

| 0.07 | (b) Frequency-domain phase noise with reference injection.                                                                     | 7      |

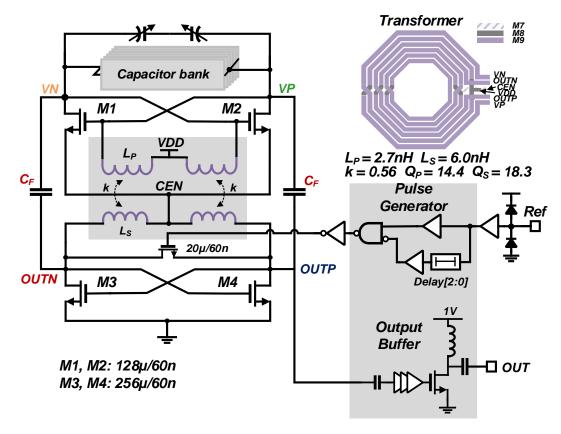

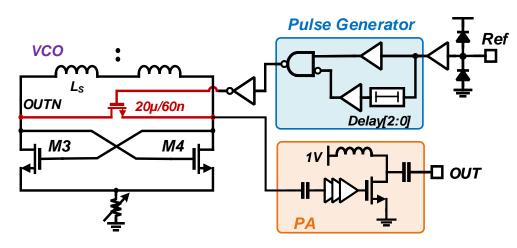

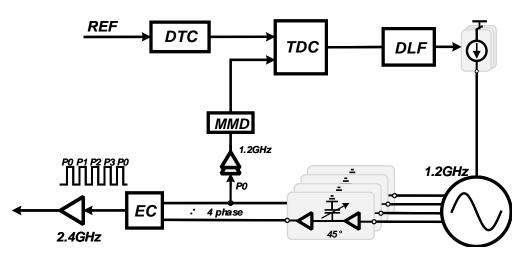

|      | Proposed ILCM with Transformer-Based VCO.                                                                                      | 8      |

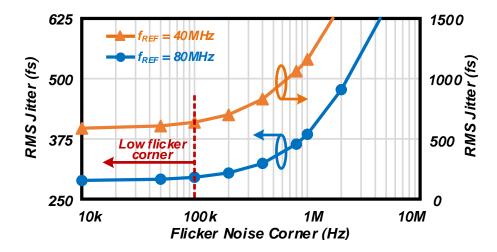

|      | Calculated jitter performance of ILCM with different VCO flicker corner.                                                       | 8      |

|      | Proposed ULP transformer-based VCO with flicker noise reduction                                                                | 8      |

|      | Schematic of capacitor bank and equivalent model of the half transformer.                                                      | 8      |

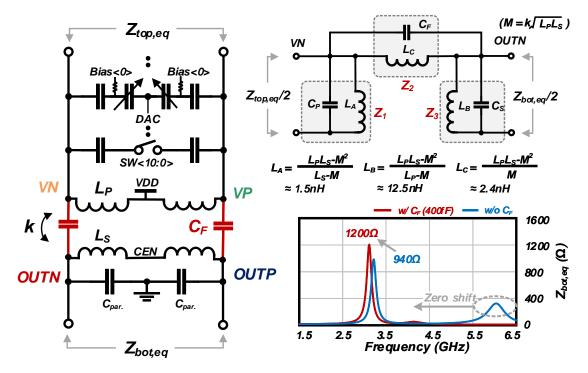

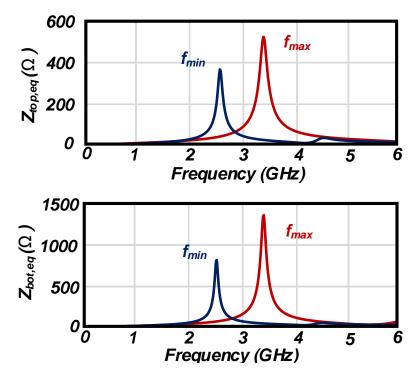

|      | Simulated tank impedance over frequency tuning range                                                                           | 8      |

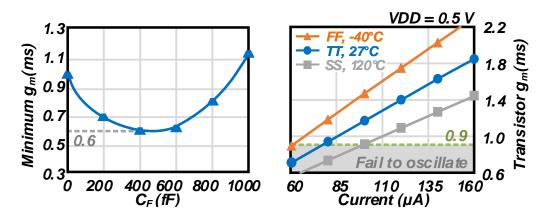

| 2.42 | Calculated minimum required $g_{m0}$ and simulated transistor $g_{m0}$ versus dif-                                             | 8      |

| 2.43 | ferent current bias                                                                                                            | 8      |

| 2 14 | current bias (160/310 µA)                                                                                                      | 0<br>8 |

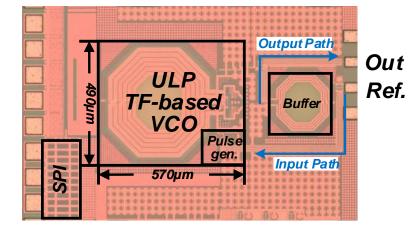

|      | Chip micrograph.                                                                                                               | 9      |

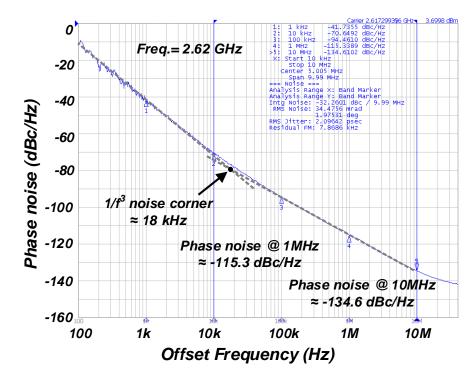

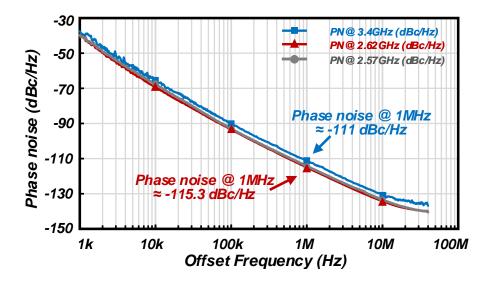

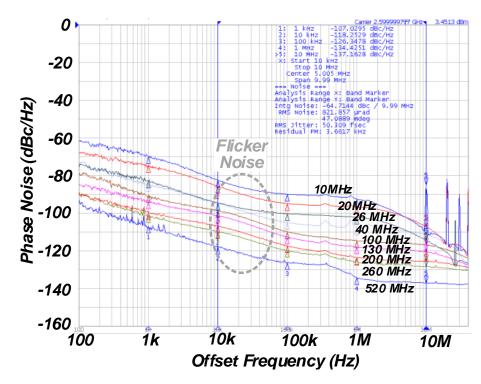

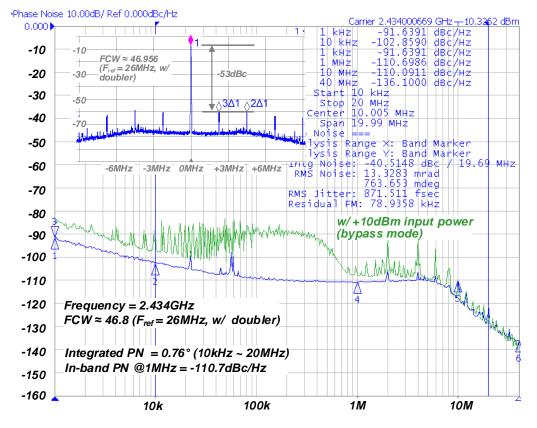

|      | Measured phase noise of the VCO at 2.62 GHz oscillation frequency                                                              | 9      |

|      | Measured phase noise of the VCO at 2.02 OH2 oscillation nequency Measured phase noise of the VCO at representative frequencies | 9      |

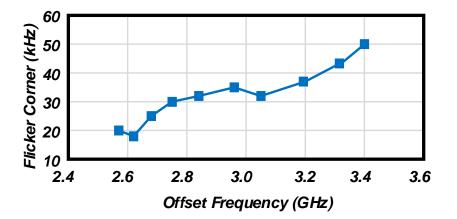

|      | Measured flicker noise corner over the frequency tuning range frequencies.                                                     | 9      |

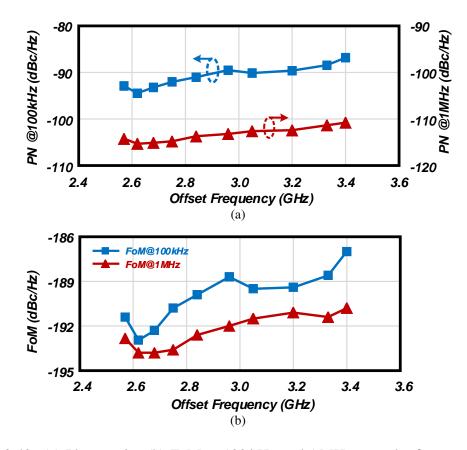

|      | (a) Phase noise (b) FoM at 100 kHz and 1 MHz over the frequency tuning                                                         |        |

| 2.17 | range frequencies.                                                                                                             | 9      |

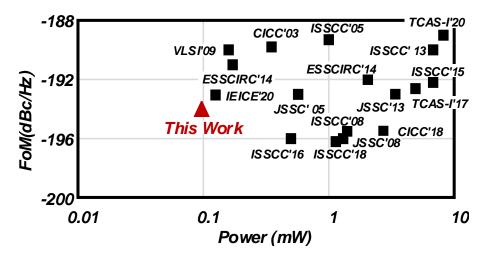

| 2.50 | Comparison of power and FoM in low-power LC-VCOs.                                                                              | 9      |

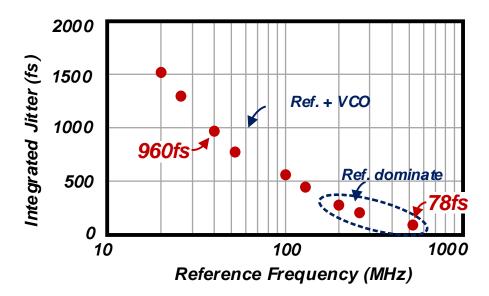

|      | Measured injection-locked phase noise with different reference frequencies.                                                    | 9      |

|      | Measured integrated jitter performance.                                                                                        | 9      |

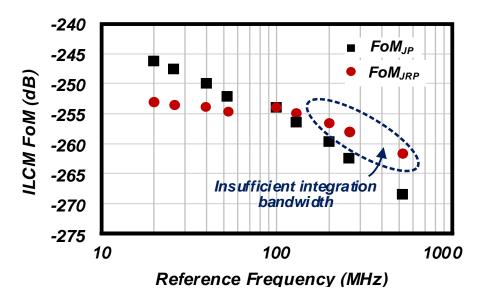

|      | Calculated FoM with different injection reference frequencies.                                                                 | 9      |

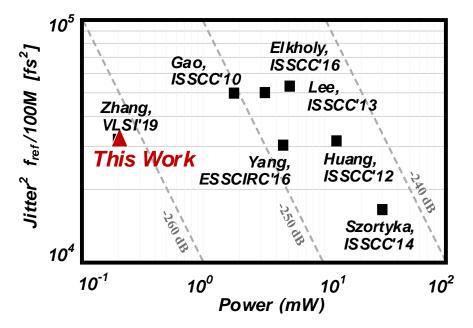

|      | State-of-the-art ILCMs.                                                                                                        | 9      |

|      |                                                                                                                                |        |

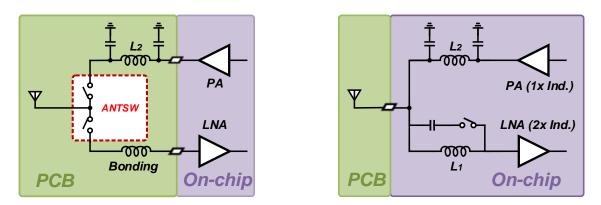

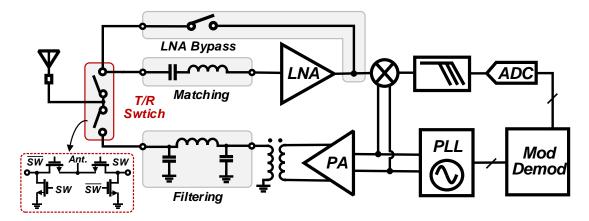

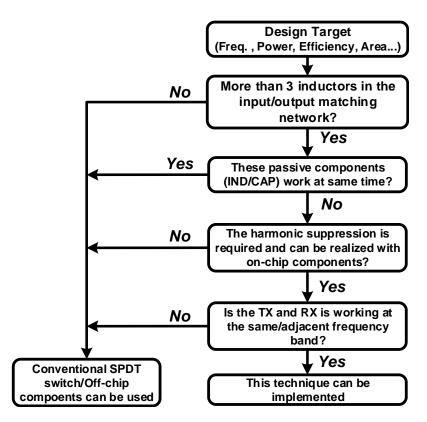

| 3.1  | BLE transceiver with conventional SPST/SPDT switch and on-chip match-        |

|------|------------------------------------------------------------------------------|

|      | ing network                                                                  |

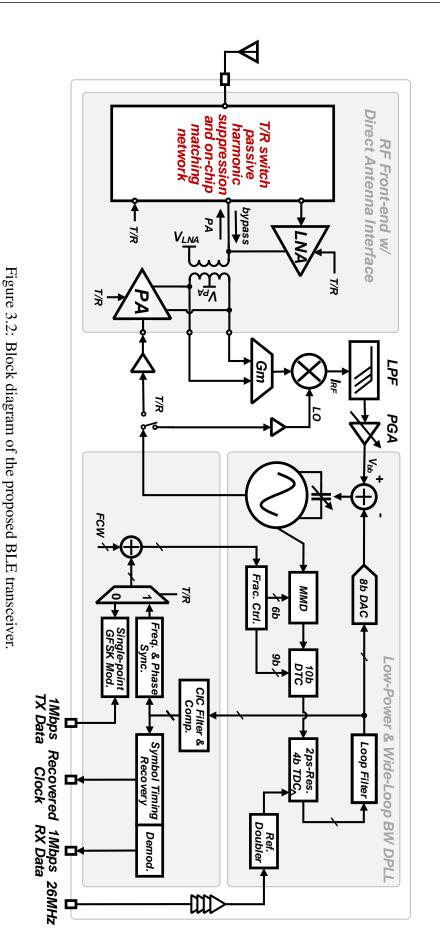

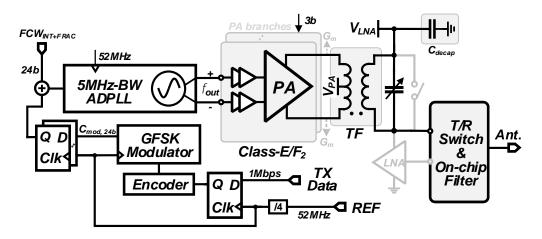

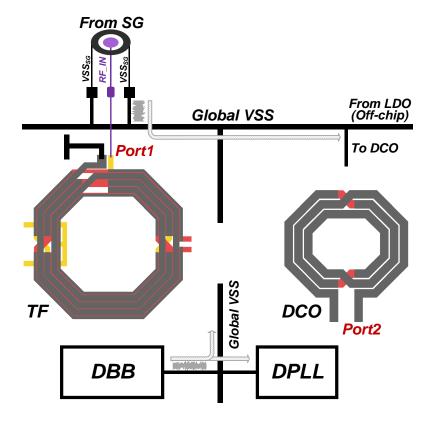

| 3.2  | Block diagram of the proposed BLE transceiver                                |

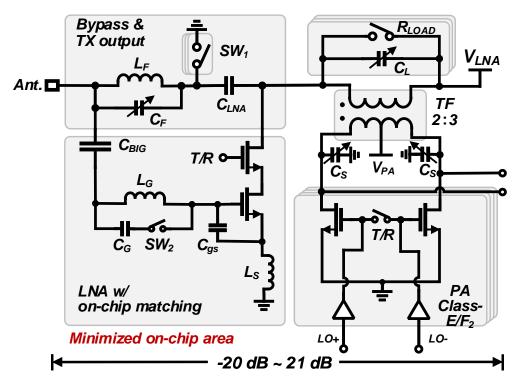

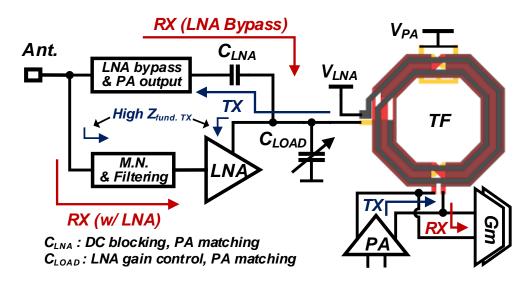

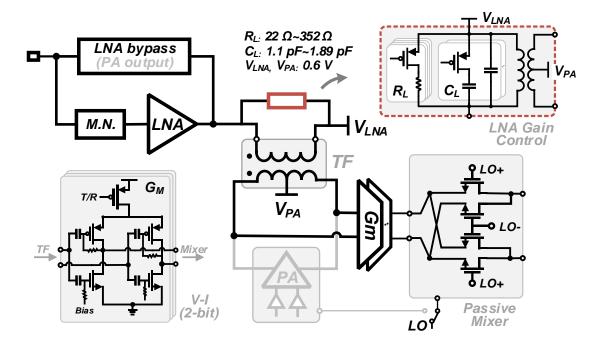

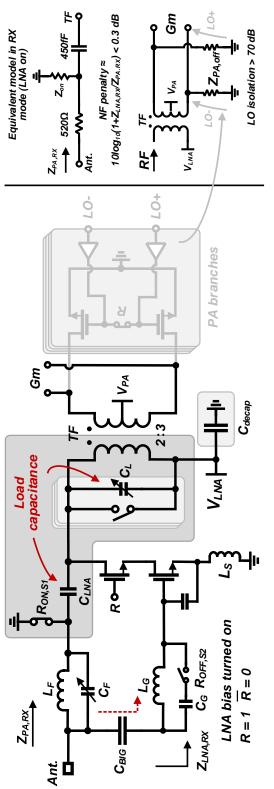

| 3.3  | RF front-end with direct antenna interface                                   |

| 3.4  | RFIO block including the LNA, LNA bypass, transimpedance amplifier           |

|      | $(G_m)$ and last stage of class-E/F_2 PA                                     |

| 3.5  | The consideration of the proposed RFIO in low-power and small-area           |

|      | transceiver design                                                           |

| 3.6  | RF building blocks including LNA, G <sub>m</sub> and passive mixer           |

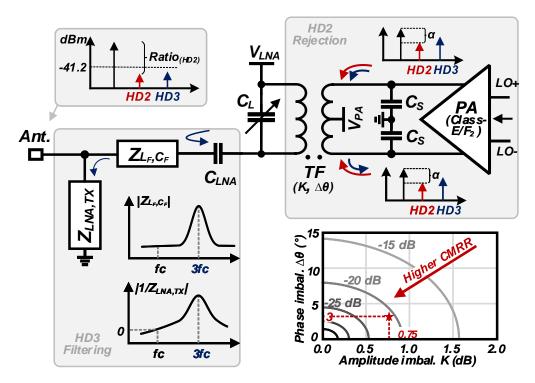

| 3.7  | Common-mode rejection with phase and amplitude imbalance and HD3             |

|      | filtering network                                                            |

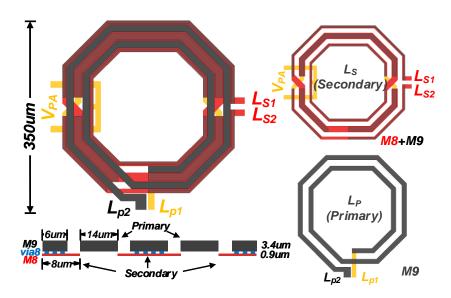

| 3.8  | High efficiency and balanced transformer with compact area 109               |

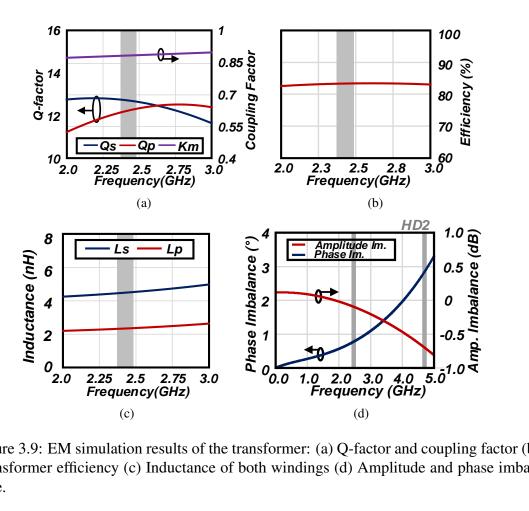

| 3.9  | EM simulation results of the transformer: (a) Q-factor and coupling factor   |

|      | (b) Transformer efficiency (c) Inductance of both windings (d) Amplitude     |

|      | and phase imbalance                                                          |

| 3.10 | BLE transceiver in RX high/mid gain mode                                     |

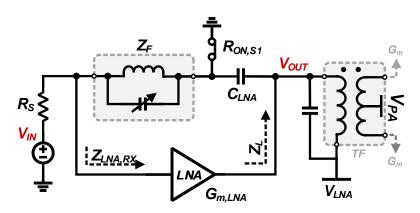

| 3.11 | Simplified LNA model with proposed RFIO                                      |

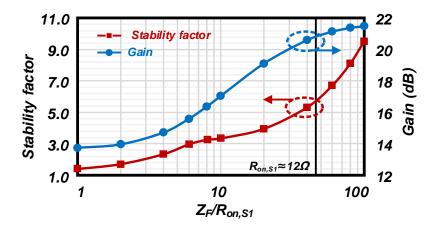

| 3.12 | LNA voltage gain and stability factor as the function of $Z_F/R_{ON,S1}$ 116 |

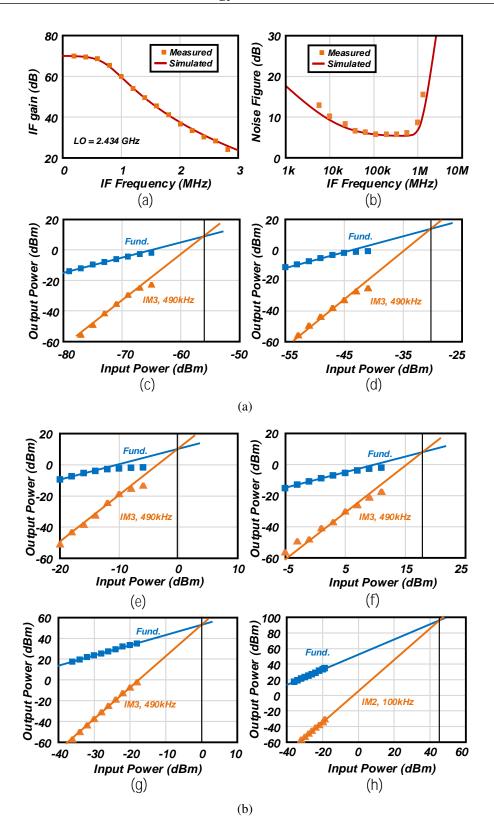

| 3.13 | RX measurement summary: (a) maximum RX front-end gain (b) mini-              |

|      | mum noise figure of the RX (c) in-band IIP3 in high gain mode (d) in-band    |

|      | IIP3 in medium gain mode (e) in-band IIP3 in low gain mode (f) in-band       |

|      | IIP3 in bypass (negative gain) mode (g) out-of-band IIP3 (h) out-of-band     |

|      | IIP2                                                                         |

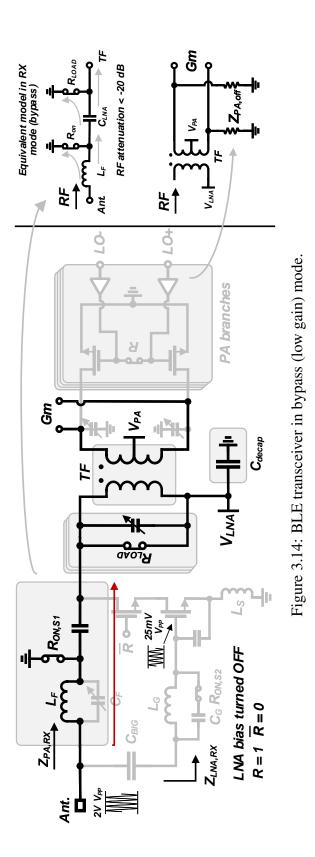

| 3.14 | BLE transceiver in bypass (low gain) mode                                    |

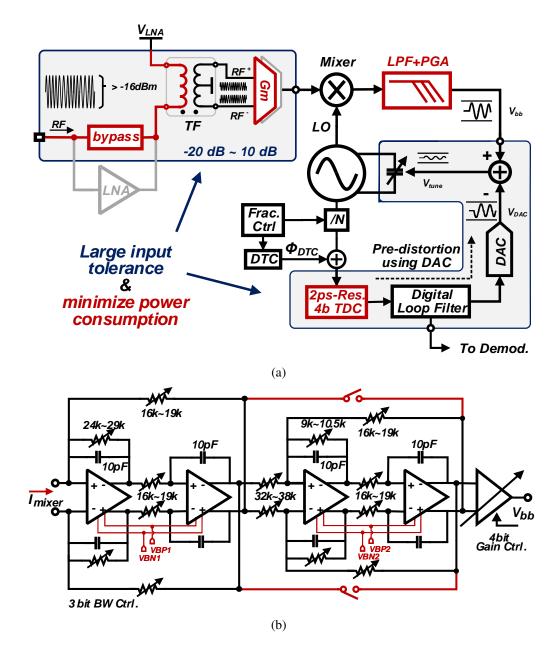

| 3.15 | (a) Large input power tolerant RX with LNA bypass route. (b) A ad-           |

|      | justable fully differential butterworth low-pass filter                      |

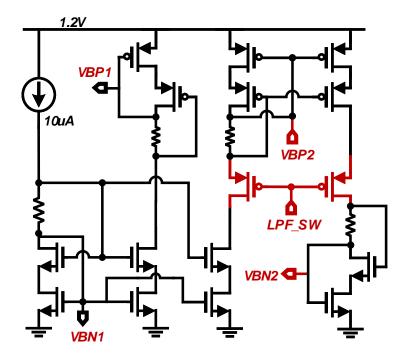

| 3.16 | Switchable cascode complementary bias circuit for LPF and PGA 122            |

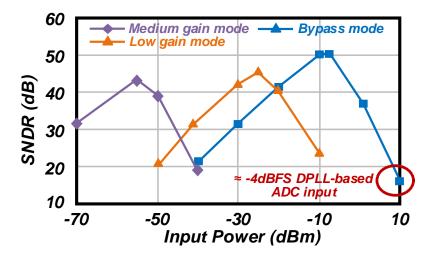

| 3.17 | Measured result of the SNDR of the front-end from the PGA output monitor.122 |

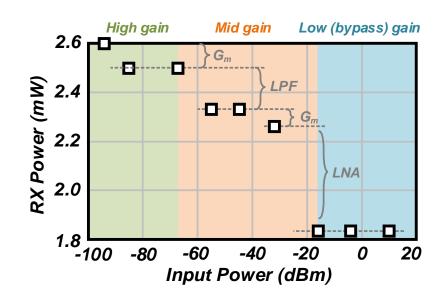

| 3.18 | RX power consumption and gain settling with different input power 123        |

| 3.19 | BLE transceiver in TX mode                                                   |

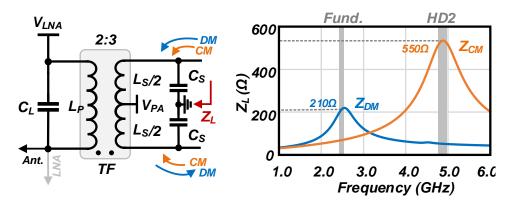

| 3.20 | Transformer-based $F_2$ tank and simulated $Z_L$ using DM/CM excitation 125  |

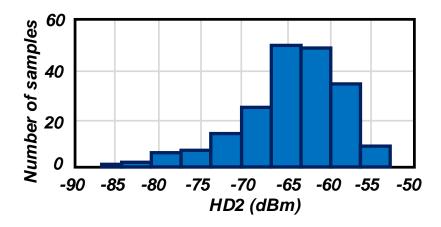

| 3.21 | HD2 of TX output in 200-run Monte Carlo simulations with mismatch            |

|      | and process variations                                                       |

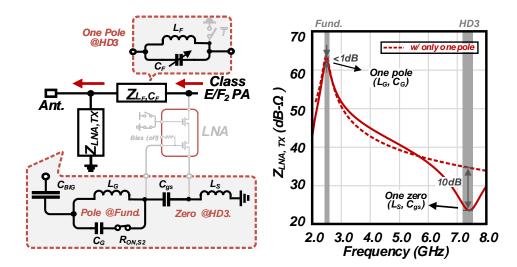

| 3.22 | The proposed HD3 notch-filter reusing LNA input matching network 127         |

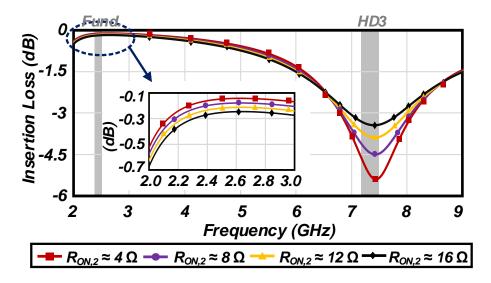

| 3.23 | Insertion loss and low-pass characteristic of RX path in TX mode 129         |

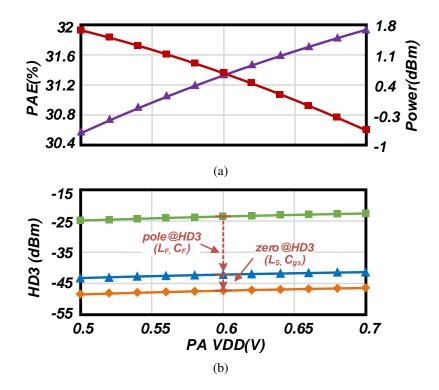

| 3.24 | Simulated (a) PA efficiency and output power versus VDD and (b) HD3          |

|      | with proposed TX matching network                                            |

#### LIST OF FIGURES

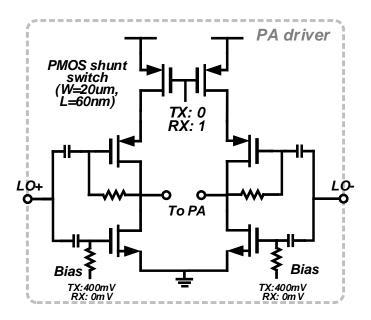

| 3.25                                                                                                  | The driver of Class-D power amplifier                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

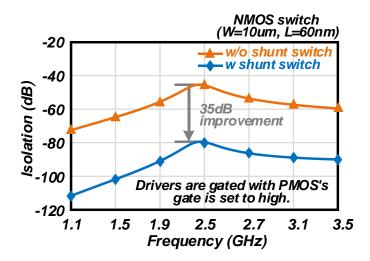

| 3.26                                                                                                  | Simulated isolation of the PA driver with and without the shunt switch $131$                                                                                                                                                                                                                                                                                                  |

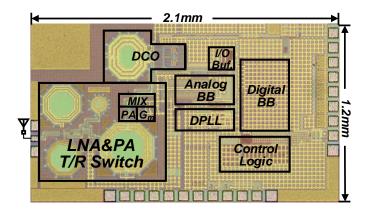

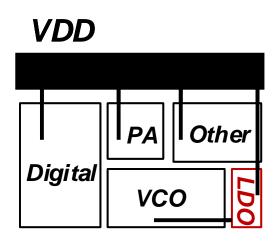

| 3.27                                                                                                  | Chip micrograph of miniaturized BLE TRX                                                                                                                                                                                                                                                                                                                                       |

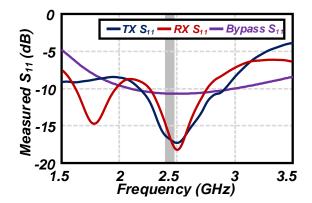

| 3.28                                                                                                  | Measured return loss in TX and RX                                                                                                                                                                                                                                                                                                                                             |

| 3.29                                                                                                  | Measured DPLL phase noise and fractional spur with 26 MHz input ref-                                                                                                                                                                                                                                                                                                          |

|                                                                                                       | erence clock (w/ reference doubler)                                                                                                                                                                                                                                                                                                                                           |

| 3.30                                                                                                  | The noise source analysis of the degradation of the phase noise performance.135                                                                                                                                                                                                                                                                                               |

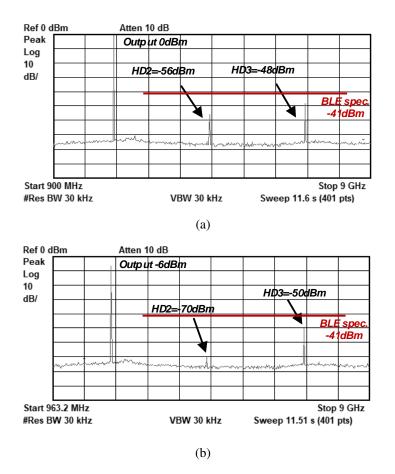

| 3.31                                                                                                  | Measured TX typical harmonic: (a) 0 dBm output power; (b) -6 dBm out-                                                                                                                                                                                                                                                                                                         |

|                                                                                                       | put power                                                                                                                                                                                                                                                                                                                                                                     |

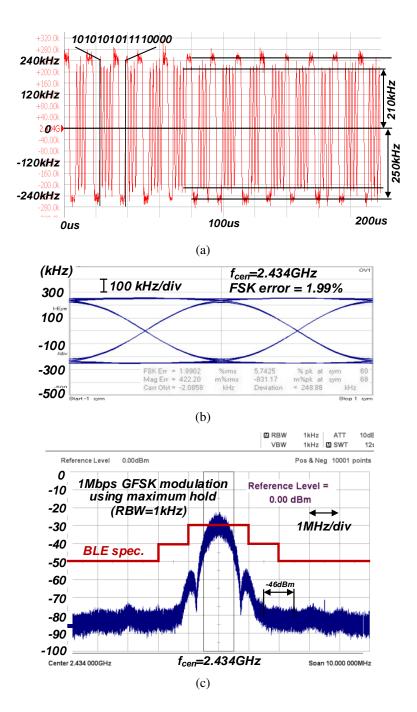

| 3.32                                                                                                  | 1 Mbps GFSK output signal spectrum at 2.434GHz using maximum hold. 138                                                                                                                                                                                                                                                                                                        |

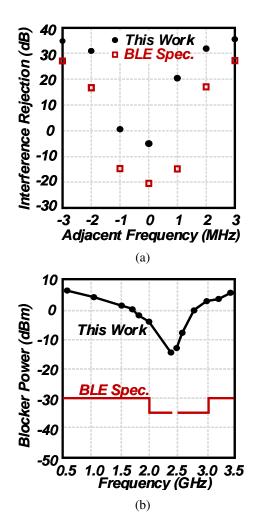

| 3.33                                                                                                  | RX measurement results: (a) ACR with -67dBm signal input; (b) out-of-                                                                                                                                                                                                                                                                                                         |

|                                                                                                       | band blocker performance                                                                                                                                                                                                                                                                                                                                                      |

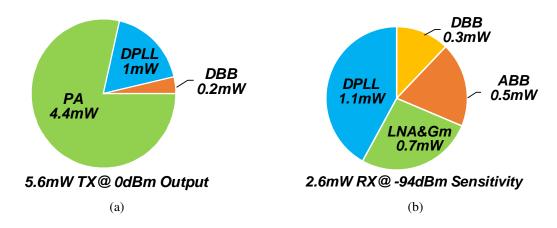

| 3.34                                                                                                  | Breakdown of measured power: (a) TX mode with 0dBm output power                                                                                                                                                                                                                                                                                                               |

|                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                       | (b) RX mode with minimum sensitivity                                                                                                                                                                                                                                                                                                                                          |

| 4.1                                                                                                   | (b) RX mode with minimum sensitivity                                                                                                                                                                                                                                                                                                                                          |

| 4.1<br>4.2                                                                                            |                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                       | Simplified Transmitter Structure Based on CRRO                                                                                                                                                                                                                                                                                                                                |

| 4.2                                                                                                   | Simplified Transmitter Structure Based on CRRO                                                                                                                                                                                                                                                                                                                                |

| 4.2<br>4.3                                                                                            | Simplified Transmitter Structure Based on CRRO                                                                                                                                                                                                                                                                                                                                |

| 4.2<br>4.3<br>4.4                                                                                     | Simplified Transmitter Structure Based on CRRO                                                                                                                                                                                                                                                                                                                                |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                             | Simplified Transmitter Structure Based on CRRO                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                           | Simplified Transmitter Structure Based on CRRO.148Power supply in conventional TX.149Current DAC implementation.150Conventional ring oscillator with frequency control bank.150Proposed current reused ring oscillator with current DAC implementation.151The inverter cell in current reused ring oscillator.152                                                             |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>              | Simplified Transmitter Structure Based on CRRO.148Power supply in conventional TX.149Current DAC implementation.150Conventional ring oscillator with frequency control bank.150Proposed current reused ring oscillator with current DAC implementation.151The inverter cell in current reused ring oscillator.152The phase noise coverage of the VCO with different modes.154 |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | Simplified Transmitter Structure Based on CRRO                                                                                                                                                                                                                                                                                                                                |

# **List of Tables**

| 1.1 | DETAIL DIFFERENCES BETWEEN BLUETOOTH BR/EDR AND LOW-               |

|-----|--------------------------------------------------------------------|

|     | ENERGY                                                             |

| 1.2 | TRANSMITTER CHARACTERISTICS BASED ON CORE SPECIFICATION            |

|     | V5.2                                                               |

| 1.3 | Receiver Characteristics based on core specification V5.2 . $\ 18$ |

| 1.4 | Summary of the T/R Switches and the Design Target. $\ldots$ 21     |

| 1.5 | THE DESIGN TARGETS OF THE LC-VCO, DIGITAL PLL AND THE              |

|     | BLE TRANSCEIVER                                                    |

| 2.1 | VCO simulation results with and without the PGS (same              |

|     | CURRENT BIAS CONDITION)                                            |

| 2.2 | VCO PERFORMANCES COMPARISON BETWEEN EMX RESULTS AND                |

|     | Measurement (same current bias condition)                          |

| 2.3 | PERFORMANCE SUMMARY AND COMPARISON WITH STATE-OF-THE-              |

|     | ART ULP-VCOs         74                                            |

| 2.4 | PERFORMANCE COMPARISON WITH STATE-OF-THE-ART OSCILLATORS 93        |

| 2.5 | Comparison With State-of-the-Art Works                             |

| 3.1 | Performances Summary of Transformer Designs 111                    |

| 3.2 | LNA SIMULATION RESULT SUMMARY                                      |

| 3.3 | Start-up Time Summary of Each Component in BLE Transceiver 131     |

| 3.4 | ON-CHIP AREA OF EACH PART                                          |

| 3.5 | THE POWER COMPARISON OF EACH COMPONENT WITH STATE-OF-              |

|     | THE-ART BLE DESIGNS                                                |

| 3.6 | Comparison of the T/R Switches                                     |

| 3.7 | COMPARISON TABLE OF THE STATE-OF-THE-ART BLE TRANSCEIVERS141       |

| 3.8 | OFF-CHIP COMPONENTS COST REDUCTION                                 |

| 4.1 | Comparison with Other State-of-The-Art BLE VCOs 152                |

| 4.2 | TRANSMITTER CHARACTERISTICS BASED ON CORE SPECIFICATION |     |

|-----|---------------------------------------------------------|-----|

|     | V5.2                                                    | 153 |

### Chapter 1

### Introduction

### 1.1 Internet-of-Things and its Available Wireless Standards

The earliest concept of network-connected smart devices originated in 1982 with a drink vending machine that reports its inventory and temperature with connected internet [1]. After several decades of development and research, the application of the Internet of Things (IoT) has been extremely expanded and innovated. Now, the IoT covers huge industries and lots of application scenarios in life, which is much different from the first originated concept with much more content. Fig. 1.1 shows several important and main application cases. Autonomous driving, also well known as a self-driving car, seems unrealizable decades ago. However, it already gradually developed and commercialized. That should thank the development of various engineering technologies, such as computer science, sensor, communication, and the Internet. At present, there are mainly two ways to realize autonomous driving. One is mainly based on the self-intelligence of the vehicle, which requires various sensors embedded and through the local brain of the car. However, these kinds of technology consume high costs and are limited by the surrounding environment. Handling the various information in a complex environment is difficult and unreliable. Another way is the Internet-based technology, in which the vehicles and monitoring equipment can be connected over the air, *e.g.*, traffic light, even the people passing by, as the Fig. 1.1 shows. With the information chain between the people, vehicles, sensor and monitor and Internet, hardware requirement is greatly reduced and robust in the complex environment. As lifestyles change, many more smart devices are applied with our human body, e.g., smartwatch with a heartbeat monitor, which can collect the data of our bodies and share with family members or even medical institutions in case of emergence. Not just the smartphones and the computers, every controllable item we can find in our

#### Figure 1.1: The concept of the Internet of Things.

house can be connected. Those devices can communicate, send useful information and take your words as commands. What we called the smart house or home automation is also based on the IoT. Take the light as an example. With an Internet-connected light bulb, the turn-on or turn-off operation can be remote and easily realized through the voice, evading the manual operation greatly. With the embedded sensor in the human body, the light control can be much more effective and energy harvested with monitoring our position in the house. Since the sensor also can collect the information of our bodies and even the mental, the light condition can be controlled to make people feel most comfortable. Body temperature also can be monitored and direct control the air conditioner and the direction of its fan. Through connection, those conventional devices in the house controlled with a smart brain with artificial intelligence help life in such a house become more comfortable.

Finally, the infrastructures of the city or big factory also can form a large wireless network. With connected through the Internet, the information can be uploaded, and each device can be monitored. That is a little bit like the first smart device introduced in the beginning. However, the content is much more complicated and different. Also, the amount of data are greatly increased because of the massive and various equipment. For example, the communication between the machines and the power devices can be useful in the management of the factory. The labor cost can be heavily reduced with the automatic power control, and also, the machine status can be monitored using a remote terminal.

All those mentioned applications and networks are greatly benefiting from the popularity of wireless Internet that enabled by a various cellular network. As already popularized WiFi network, the small network with an available wired network interface will be easier to connect to a gateway device by using devices like WiFi routers. Moreover, the WiFi router will be connected to a large cellular network connected by fiber optic or 5G network. Finally, all the devices in the small networks can form a massive device's network. With the help of the computing sources such as cloud servers or smart terminals, a large amount of data can be further processed and feedback to the devices to make life better. An era full of smart devices is approaching, which can give anyone a better life if the IoT and the required wireless techniques can be further developed and exploited.

#### 1.1.1 Medium-Range and Long-Range Wireless Standard

**LTE-Advanced:** Conventional LTE is known as 3.9G of telecommunications developed by the 3GPP (3rd Generation Partnership Project). In telecommunications, this one was also promoted with the name "4G LTE". The initial LTE does not meet the technical criteria of a 4G wireless service, as specified by the 3GPP (Release 8 and 9 document series for LTE Advanced). Since 2011, the LTE-Advanced standard has been commercialized. This standard uses several frequency bands (from around 1 GHz to 6 GHz) with associated different bandwidth.

**5G:** As well know, 5G is the fifth generation technology standard for cellular networks. The low-band of 5G (FR1) uses a similar band as the LTE (<6 GHz). While the new 3GPP specification series 38 provide more technical details. In the newly released 5G NR standard, high-band 5G (FR2) uses frequencies from 25 GHz to 39 GHz, almost achieve the millimeter-wave band. However, higher frequencies may be used in the future. This standard targets much faster wireless communication, such as gigabit per second. Not like the millimeter wave standard, which has a much-limited communication distance, the 5G NR can be applied in medium-range telecommunications, and has been firstly commercialized in 2019.

NB-IoT: It is also standardized by the 3GPP (release 13). This standard uses the LTE

technology subset but with much narrow bandwidth (200 kHz). This standard mainly focuses on the coverage range and the connection density.

**Long-range Communication:** There are several standards for long-distances communications, such as LPWAN. These standards typically use ultra-narrow bandwidth and ultra-low data rate, *e.g.*, 0.3 kbit/s.

#### 1.1.2 Short-Range Wireless Standard

**WiFi**: It has family standards based on the IEEE 802.11, and this standard has been developed for more than twenty years. It operates at the ISM band in the sub-6 GHz, which including the 2.4 GHz, 3.6 GHz, and 4.9/5.0 GHz bands. A high date rate can be realized from several Mbps to several Gbps. This standard is straightforward to be implemented with a wired network interface within a few tens of meters. For the newly released WiFi 6 standard, which is based on IEEE 802.11ax, a higher-order modulation method has been implemented, and a higher data-rate can be achieved.

**ZigBee:** It is a short-range wireless standard based on the IEEE 802.15.4. This standard operates in the 2.4 GHz ISM-band with 250 kbps data rate suitable for the intermittent data transmission from the sensors and duty-cycled devices. The maximum number of nodes in the Zigbee network is 1024. Depend on its working environment and power configuration. The communication range can be controlled from tens of meters to hundreds of meters.

**Light Fidelity:** A communication method utilized the light emitted by diodes (LEDs) as the information carrier. Due to the characteristics of visible light itself, this standard can be effective in confidential communication that can't get through the wall or the door. Moreover, this standard is useful in the special situation without causing electromagnetic interference such as hospital and the airplane.

**NFC:** Near-field communication is a protocol for two devices which has a short distance lower than 4 cm. This protocol is well known because of the identity cards and the contactless payment. In a current new type of mobile phone, the NFC is integrated, which can be used for mobile payment and the trancar ticket like the PASMO.

Bluetooth Classic: As the most famous wireless standard within tens of meters, Blue-

Figure 1.2: The channels of Bluetooth standard and its coexistence with Wi-Fi.

tooth has been widely used in electronic devices around us, such as the mobile phone and headphone. This standard has been proposed since 1994 and has been iterated and upgraded into several versions. This standard operates at 2.4GHz, which is located in the globally unlicensed ISM frequency band. The variable data rate and robust implementation make this standard widely used in audio streaming and file transmission.

**Bluetooth Low-Energy:** Different from the classic Bluetooth standard used for continuous audio streaming, Bluetooth Low-Energy (BLE) is an ultra-low-power version of Bluetooth (4.2). The main target devices are the applications that do not require continuous connection and intermittent data transmission, *e.g.*, disposable sensors, but depend on long battery life and costs.

#### **1.2** Bluetooth Transceiver and its Applications

After decades of evolution from 1994, *Bluetooth* technology becomes one of the most popular wireless standards in short and middle-range communications using short-wavelength UHF radio waves in the ISM bands, from 2.4 GHz to 2.4835 GHz. The RF channels are specified to 1 MHz, while the band each channel is 2 MHz. Together with WiFi technology, it is widely adopted in almost all kinds of wireless communications. As shown in

Fig. 1.2, three advertising channels (channel 37, 38, 39) for the device discovery, connection establishment, and broadcast transmissions. To robust co-exist with the WiFi signal working on the same ISM band, which has a much wider channel bandwidth. A mechanism called adaptive frequency hopping is adopted. This mechanism is used by the link layer, and the link-layer will remap a given packet from a known bad channel to a known channel without interference, *e.g.*, a WiFi signal. Through that, interference from other devices is reduced. This technology really makes the Bluetooth transceivers robust work in the complex environment where the microwave oven, other Bluetooth devices, and WiFi devices co-exist. Because of its robustness and easy implementation, the Bluetooth transceivers have become much popular with various applications.

For now, the most famous application scenario is the smartphone integration and replacing the conventional wired solutions, such as earphones and keyboards *etc.*. For the Bluetooth standard beginning, the Institute of Electrical and Electronics Engineer (IEEE) standardized this standard as IEEE 802.15.1 at the beginning of this century. However, it is no longer maintained by IEEE. Now a special interest group (SIG) [2] oversees the development of these standards as well as protects the trademarks. It was established by IBM, Intel, Nokia, and Toshiba, and later joined many other companies. Now, the Bluetooth SIG is a global community of over 36,000 companies serving to unify, harmonize and drive innovation in this Bluetooth standard. In order to meet the requirement of the market and uniform standards, the manufacturer or the developer must satisfy Bluetooth SIG standards before releasing to the market.

Also, because of the Bluetooth transceiver work in the ISM band, which is a globally unlicensed frequency band, the transceiver implementation also must satisfy the regulations required by the local government, such as the Federal Communications Commission (FCC) in the United States. For example, the transceiver operating with the frequency band from 2400–2483.5 MHz must satisfy the FCC 15.247. Otherwise, any devices with the substandard Bluetooth transceiver cannot be sold in the United States.

The core specification has been updated from version 1.0 (1998) to version 5.2 (December 2019). In the standard V4.0, the low-energy controller part is added, which has many differences from the previous basic rate (BR) or enhanced data rate (EDR) controller. The conventional Bluetooth addresses the point-to-point communication, such as the audio streaming for the laptop to the audio speaker shown in Fig. 1.3. The high sound quality requires the higher data rate of the Bluetooth transceiver. Typically, the Bluetooth basic data rate mode with 1 Mbps and enhanced data rate 2/3 Mbps mode are sufficient for these applications.

Bluetooth Application

Figure 1.3: The applications of Bluetooth and its classification.

There are several important differences of the Bluetooth Low-Energy listed below.

**Lower Power:** The low duty cycle such as 0.5 s to 10 s intervals. The scenarios for which the period of interaction is large, and there is a very relaxed latency. The temperature and humidity monitoring are the typical scenarios. The leakage power of the transceiver is also design low. Thus, the average power consumption is quite small, which can be clearly expressed by the following equation.

$$DC_{\rm AVG} = \frac{DC_{\rm operation} \times T_{\rm DC} + DC_{\rm leakage} \times (T - T_{\rm DC})}{T}$$

(1.1)

From this equation, different optimizations for low power consumption to achieve a long lifetime can be taken into different scenarios [3]. For example, a continuous high frequency is scenarios for which the operation cycle dominates, *e.g.*, heart rate monitors that communicate measurements several times in seconds to trackers. More accurate counting requires more operation cycles in seconds, which is a trade-off with the operation power. Thus, the DC power for the operation should be optimized. Another periodic low-frequency scenarios are the applications that have a long standby time, *e.g.*, temperature monitoring, which has a gradually transformation. In this kind of application, the operation cycle can be very small such as one cycle (<10 ms) in tens of seconds. The leakage power of the transceiver will dominate the total average power consumption.

| Characteristic           | Bluetooth BR/EDR      | Bluetooth Low-Energy* |

|--------------------------|-----------------------|-----------------------|

| Discovery                | Inquiry               | Advertising           |

| RF Channels              | 79 Channels           | 40 Channels           |

| Number of Piconet Slaves | 7(active)             | Unlimited             |

| Modulation Method        | GFSK/DQPSK, 8QPSK     | GFSK                  |

| Max Data Rate            | 1/2,3Mbps             | 1Mbps                 |

| Typical Range            | >10 meters            | >10 meters            |

| Output Power             | $100 \text{ mW}^{**}$ | $100 \text{ mW}^{**}$ |

Table 1.1: DETAIL DIFFERENCES BETWEEN BLUETOOTH BR/EDR AND LOW-ENERGY

\* Core version 5.2

\*\* Power Class I

**Faster Connection:** The low-power consumption is a benefit from its fast connection operation. For a classic Bluetooth transceiver, a link-level connection can take up to 100 ms, which means more power is wasted in the long connection progress. For a BLE transceiver, the devices can connect and send and acknowledge data in 3 ms. That requires the BLE transceiver has a much faster mode switch function, which can send and acknowledge data individually.

Table 1.1 summarized the detailed differences between Bluetooth BR/EDR and Low-Energy. While the Bluetooth BR and EDR address the point to point communication. The Bluetooth expanded into broadcast communications to enable indoor positioning and location services, as shown in Fig. 1.3.

BLE devices support several roles in these applications,

**Data transfer Application:** The smartwatch performs a master device that scans for advertisers. If there is a new message comes, the smartphone will operate as the advertiser. The connection between the phone and watch can be initiated since the BLE is designed with a faster connection. This application can be effective in the broadcast in crowded places.

**Locations Services:** Several position fixed beacons will be placed surround. This function relies on a property known as the received signal strength indicator (RSSI) to calculate how close a beacon is from the device. According to the beacon number, more precision can be realized.

Figure 1.4: The market volume of BLE applications and its trend.

**Mesh Network:** Since the BLE is designed as a reliable wireless solution to establish large-scale device networks. A mesh network can be established with the BLE. This concept originated from a massive network. The topology is that one of the "node" (device) transmits its own data, and this device also serves as the relay for the nearby "node". All the nodes can be practices to form the most efficient data transmission path. Even, some failures happen in some "nodes", the other path through the working "node" will still continue to deliver the information. That ensures the connectivity is always working and reduce the cost from the failure nodes.

The variety of the roles and features present very good support for different application scenarios with low distance and moderate/slow date rate. It is the main reason that Bluetooth standard with additional BLE becomes one of the most popular wireless technology for IoT applications. From the data website Statista 2020, as shown in Fig. 1.4, the BLE market volume has been increased from 1.6 billion in 2013 to nearly six times until now. And it can be predicted from the data, the marker volume of the BLE will still increase and break the 10 billion record, which no other standards can reach. The emerging new applications such as the True Wireless Stereo (TWS) earphone and home automation boost the accelerated the market volume growth of BLE.

### **1.3** Challenges for RF Front-End Design with Direct Antenna Interface

#### **1.3.1** General Challenges for BLE TRXs

The general challenges for BLE transceivers are considered for both industry and academic aspects.

**Low Cost:** The cost is the main important point for the low-end Bluetooth manufacturers to enter the market. Low-price means more market share while increasing shipments. The increased shipments help further reduce costs. Furthermore, this positive feedback will allow a company to beat others to occupy all low-end market shares.

**Low-Power Consumption:** The power consumption for the BLE application is also important, which will be mainly used in wearable devices and wireless sensors. Those devices do not need to keep running at all the time, and they are only wakened up to perform data transmission for a short time. However, due to the size limitation according to the application scenario, a long lifetime is desired with a small battery capacity. That requires the BLE transceiver works with low-power consumption and low stand along with power.

**Small Module Size:** As mentioned before, the main applications of the BLE transceiver include wearable devices and sensors. In the real application, the module of the BLE transceiver includes the PCB, and the off-chip components (*e.g.*, trace antenna) takes a much larger area but with lower cost. Some kinds of BLE modules integrate internal antenna, which reduces off-chip area but increases the module cost.

**Signal Accuracy and Stability:** For the high-end market, a stable and excellent performance will be more important. Such for the indoor positioning, and accuracy RSSI is required. That means the TX power should be precisely controlled, and RX demodulation should be very accurate overall for possible environmental changes.

**Low latency and fast link:** A shorter link establishment also means lower power consumption with reduced operation time. Meanwhile, the interference will cause the performance degradation of the BLE transceiver, which will heavy the latency of BLE communications. This kind of performance is also a mark for high-end BLE products.

Figure 1.5: The general structure for wireless transceivers.

#### **1.3.2** Academic Challenges

In this thesis, only academic challenges listed below are mainly considered due to personal ability and time constraints. The other aspects without here can be considered as future upgrades or work in the industry.

**Lower Cost:** As an industry product, the BLE modules must have stable performances, and typically, the conventional structure of circuits will be applied to reduce the risks while trading with the on/off-chip area. However, in academia, the new circuit structure can be tried without considering commercialization. Meanwhile, the off-chip components are typically implemented to reduce the difficulty of full integration and avoid performance degradation. In here, we mainly consider the feasibility of reducing the off-chip components and try to realize the nearly same performance with reduced off-chip component numbers and smaller on-chip area.

**Lower Power Consumption:** The low-power techniques are seldom reported by the industry company. It's not to say that they don't have low-power technologies, but that they often add a lot of power in order to obtain stable performance. In academic consideration, the feasibility of the lower power consumption method can be certified with new circuit techniques.

#### **1.3.3 Fundamental Issues**

For IoT applications, large-scale popularization will inevitably require cost reduction of wireless transceiver modules, including the IC cost and PCB cost. As we know, there are mainly three types of IC cost, which includes the die cost (> 50%), testing cost, and the packaging cost. The die cost is determined by the wafer cost and the number of dies per wafer. That means the small chip area will reduce the average IC cost. This saving will be more evident for more advanced processes. The implementation of off-chip components can realize very outstanding performances. However, it is inevitably to increase the PCB cost and finally increases the module cost.

Fig. 1.5 shows the general structure of wireless transceivers. As we know, the passive components cannot be shrunk with the process scaling. Moreover, these components occupy most of the on-chip area because of the large inductors are required in these circuits, such as our LC-type oscillator. Meanwhile, for the oscillator, specified phase noise must be satisfied to achieve the target transceiver performances (the detailed PN performance required will be discussed in the next sub-section). Typically, for the low-power IoT application, the phase noise performance is not critical. Meanwhile, the on-chip area becomes much important because of the cost.

Another one that takes up much on-chip area is the RF input and output circuits. These circuits, such as LNA, PA, and switches, can be designed with off-chip components. However, that will heavily increase the off-chip costs and area. Typically, for the LNA, at least three inductors are required (for the cascode LNA), and at least two inductors are required for the PA (class-D PA with LC-notch filter). The total number of inductors is almost unchanged in the conventional design. Meanwhile, to share a single antenna, the antenna switch must be integrated by using on/off-chip switches. In this thesis, we mainly focus on how to realize a low-power design while reducing the on-chip area by reusing the passive components (not limited to inductors) and mitigating the usage of off-chip components. We want to realize a fully integrated BLE transceiver with minimized the on-chip area and power consumption while meeting the FCC requirements.

Thus, to reduce the cost of the wireless transceiver as much as possible so that it can be popularized in life, this thesis focuses on the small-area front-end design, including the RF input/output circuit and frequency synthesis circuits.

#### **1.3.4** Specification Consideration

Fig. 1.6 shows an example of a BLE transient power breakdown from a commercial SoC (CC-series, Texas Instruments). The transceiver will be waked up by the triggers from the wake-up receiver embedded. And then pre-process will start. Before the receiver works,

Figure 1.6: Power breakdown of a Texas Instruments CC-series BLE device in a single connection event.

there is a pre-RX procedure to configure the transceiver into the receiver mode. After the desired signal is received, the transceiver will be re-configured, and then the TX will start to work, which sends the data out as the response of the received signal. From Fig. 1.6, the power consumption of the transceiver is clearly shown. As explained in Chapter 1.2, for the a continuous high-frequency scenarios, the power of the operation cycle dominates the average power consumption and thus the lifetime. For a conventional 2.4 GHz transceiver, there are a lot of low-power techniques to lower the power consumption. However, as a globally unified standard, the Bluetooth Low-energy transceiver must satisfy the core specification. Only considering the specs and the power budget at the same time, power reduction is effective. Firstly, the analysis of the difficulties of BLE specification and transceiver implementation should be carried.

Transmitter Characteristics based on core specification V5.2 [4] are summarized in Table 1.2. Total 40 channels are assigned from 2.4 GHz to 2.8 GHz with 2 MHz channel spacing. However, the output power is enhanced and multiple classes are selectable. Also the data rate is not fixed to the 1 Mbps and a 2 Mbps is also as one of the options in V5.2. The 1 Mbps, as the must-have option, has the signal energy concentrates from -500 kHz to +500 kHz. For each channel, there are 500 KHz exists on the left and right side of the signal, which relax the adjacent channel interference performance for the RX. For the 1 Mbps option, because of the larger signal bandwidth (2 MHz), the channel bandwidth is also increased to 4 MHz, which includes two 1 MHz blank existing on the left and right side. The frequency deviation, as shown in Fig. 1.7, is also specified to different data rate options. What should be noticed here is the minimum frequency deviation test method, which is also specified in the specification. With a data pattern 00001111, the F<sub>min</sub> must

| Parameters                                     |                          | Value                          |

|------------------------------------------------|--------------------------|--------------------------------|

|                                                |                          | f=2402+k*2 MHz,                |

| Channels                                       |                          | (k=0, ,39)                     |

|                                                |                          | Power Class 1:10dBm~+20dBm     |

| Output Power                                   |                          | Power Class 1.5: -20dBm~+10dBm |

| Output I ower                                  |                          | Power Class 2:-20dBm~+4dBm     |

|                                                |                          | Power Class 3: 0dBm~-20dBm     |

| Modulation Sche                                | me                       | GFSK                           |

| wiodulation Sche                               |                          | $(0.5\pm5\%$ modulation index) |

|                                                |                          | 1 Mbps: 250 KHz                |

| Frequency Devia                                | tion                     | (F <sub>min</sub> >185 KHz)    |

| $F_{\min} = \min \{  F_{\min+} , F_{\min-} \}$ |                          | 2 Mbps: 500 KHz                |

|                                                |                          | (F <sub>min</sub> >370 KHz)    |

| Harmonic Emission                              | 2 <sup>nd</sup> harmonic | -41.2 <sup>*</sup> dBm         |

| Harmonic Emission                              | 3 <sup>rd</sup> harmonic | -41.2* dBm                     |

|                                                | 1 Mbps                   | 2 MHz: -20 dBm                 |

| In-band Spurious Emission                      | 1 Mbps                   | $\geq$ 3 MHz: -30 dBm          |

| In-baild Spurious Emission                     | 2 Mbps                   | 4,5 MHz: -20 dBm               |

|                                                | 2 10005                  | $\geq$ 6 MHz: -30 dBm          |

|                                                | Dackage                  | $\pm$ 50 kHz                   |

| Frequency Drift                                | Package                  | (Maximum drift)                |

|                                                | Drift Rate               | 400 Hz/µS                      |

#### Table 1.2: TRANSMITTER CHARACTERISTICS BASED ON CORE SPECIFICATION V5.2

\* According to FCC 15.249.

Figure 1.7: The TX frequency deviation of BLE Transmitter.

have an average value between 225 kHz to 275 kHz. With a data pattern 01010101, the  $F_{min}$  must be large than 185 kHz with the average value large than 0.8 times the average value of pattern 00001111.

The TX in-band spurious emission is generated from the non-linearity of the TX chain or the phase noise or spurious of the frequency generators (PLLs). What should be noticed that the in-band spurious emission is specified in absolute value (dBm), which is measured on a 1 MHz RF frequency range. That means with a high noise level frequency generator can't satisfy this requirement due to its noise skirt. Also, this requirement has a linear relationship with the output power. For example, for a 0 dBm output power case, the PN noise requirement of the PLL is around -100 dBc/Hz at 1 MHz offset to satisfy the in-band spurious emission. However, this noise performance must be improved to 20 dB higher (-120 dBc/Hz) if the output power is increased to 20 dBm. For a -100 dBc/Hz at 1 MHz frequency offset, a ring oscillator (RO) with around -86 dBc/Hz (with 5 MHz PLL bandwidth) can realize this performance. However, the phase noise of RO can't satisfied the high output power case which is difficult to achieve lower than -100 dBc/Hz at 1 MHz frequency offset. Also, the fractional spur of the PLL should be considered, which falls in the close-in frequency band. That makes the phase noise performance of PLL much tighter and safety margin should be left for a robust application (< -125 dBc/Hz at 1 MHz for 20 dBm output case).

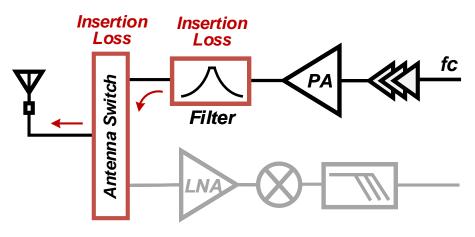

TX generates electromagnetic (EM) radiation at unintentional frequencies, and the strong harmonic spurious emissions result in polluting of the out-of-band spectrum potentially, which desenses the RXs operating at the same harmonic frequency (e.g., HD2 of the 2.4 GHz TX locates band n79 for 5G NR). Actually, the harmonic emission is not directly specified by the core specification. The only requirement is that the equipment manufacturer is responsible for the ISM out-of-band spurious emissions requirements in the intended countries of sale, such as North American or Asia market. Typically, the FCC 15.249, which specified for the transceiver which utilizes the ISM band should be satis-

Figure 1.8: The simplified transmitter model.

fied. According to the authors' knowledge, the requirement for the ISM bands transceiver is also similar as the ETSI standard (ETSI EN 300 328). The specified field strength of harmonics  $E_0$  is in micro-volts/meter (500  $\mu$ V/m specified at a distance of 3 meters) in the FCC standard, which can be converted into an equivalent -41.2 dBm as a conducted power (equivalent, sometimes "effective", isotropically radiated power, EIRP) using the following equation.

$$EIRP(dBm) = E_0 + 20log_{10}D - 108.4$$

(1.2)

The corresponding electric field strength  $E_0$  specified in FCC 15.249 is 500  $\mu$ V/m, which equals 53.98  $dB\mu$ V. This field strength limit is specified at a distance *D* equals to 3 meters. The detailed spurious emission is shown in Fig. 1.9. Because of the out-ofband spurious emission is also specified in dBm, which means the fundamental signal to harmonic distortion (HD) ratio has to be also increased. For example, in the 0 dBm output case, the second harmonic distortion (HD2) ratio is -41.2 dBc. However, this value should be increased to -51.2 dBc in the case of +10 dBm output power. That increases the difficulty of the on-chip integration due to the insufficient quality factor of the on-chip filters, which introduces large insertion loss, as shown in Fig. 1.8. Also, we should notice that power loss is inevitable in the filter implementation. It should be noticed that the on-chip filters take more chip area while off-chip filters take more PCB (off-chip) area. Neither way is economical and what we want to see today in pursuit of device miniaturization.

As the maximum frequency drift is specified in the package transmission ( $\pm$  50 kHz), this requirement, which is not strict, relaxes the local oscillator (LO) specification. Even a free-running LC-type voltage control oscillator (VCO) can satisfy this requirement due to the short length of the package in BLE (maximum size link layer data packet, 27 bytes

Figure 1.9: The TX spurious emissions including in-band and out-of-band cases.

| Parameters                 | Value          |         |

|----------------------------|----------------|---------|

| Sensitivity                | Spec.          | -70 dBm |

| Sensitivity                | Target         | -90 dBm |

| Maximum Input Power        | Spec.          | -10 dBm |

|                            | Target         | +10 dBm |

| Packet Error I             | 30.8%          |         |

| (Bit Error Ra              | (0.1%)         |         |

| Adjacent Channel Rejection | 0 MHz          | -21 dB  |

|                            | 1 MHz          | -15 dB  |

|                            | 2 MHz          | 17 dB   |

|                            | 3 MHz          | 27 dB   |

| Blocker                    | 30~2000 MHz    | -30 dBm |

|                            | 2000~2400 MHz  | -35 dBm |

|                            | 2500~3000 MHz  | -35 dBm |

|                            | 3000~12.75 GHz | -30 dBm |

Table 1.3: RECEIVER CHARACTERISTICS BASED ON CORE SPECIFICATION V5.2

of data in a 41-byte payload, which takes  $328 \mu s$ ) [5].

The summary of RX part specification are listed in the Table 1.3. The actual receiver sensitivity level is defined as the receiver input level for which specified in Table 1.3 (0.1% BER or 30.8%PER) is achieved. Firstly the received power of the BLE transceiver should be considered. To derive the received power at the input port of the receiver, the Friis transmission equation can be utilized.

$$P_{\rm R} = \frac{P_{\rm T} G_{\rm T} G_{\rm R} \lambda^2}{(4\pi D)^2} \tag{1.3}$$

$P_{\rm R}$ : received power at the input port of the receiver.

$P_{\rm T}$ : transmitted power of the output port of transmitter.

$G_{\rm T}$ ,  $G_{\rm R}$ : antenna gain in the direction of the another device.

D: Distance between the transmitter and the receiver.

$\lambda$ : The wavelength of the transmitted signal, which equals to c/f (c: speed of light).

The terms in equation (1.3) that is independent of all the hardware,  $\frac{\lambda^2}{(4\pi D)^2}$ , is defined as the Free-Space Path Loss (FSPL).

$$FSPL = \left(\frac{4\pi D}{\lambda}\right)^{2} = \left(\frac{4\pi Df}{c}\right)^{2}$$

(1.4)

$$(dB) = 20\log_{10}D + 20\log_{10}f - 147.55$$

in which, the D is in meters and f is frequency in Hertz.

To classify the relationship between receiver power  $P_R$  and the FSPL, it is useful to rewrite the equation (1.3) in decibel, which has:

$$P_{\mathbf{R}}(\mathbf{dBm}) = P_{\mathbf{T}}(\mathbf{dBm}) + G_{\mathbf{T}}(\mathbf{dB}) - FSPL(\mathbf{dB}) + G_{\mathbf{R}}(\mathbf{dB})$$

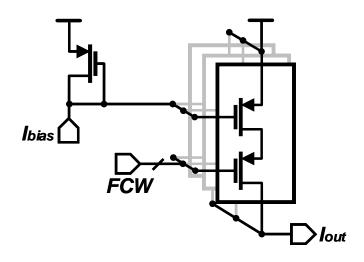

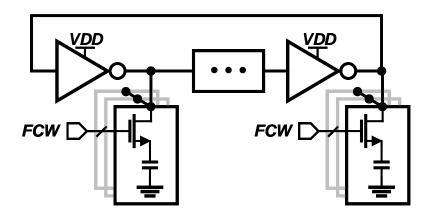

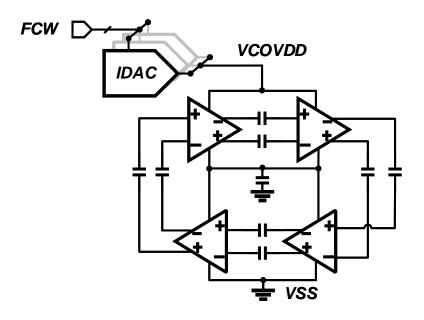

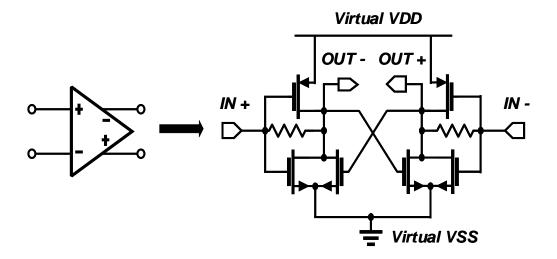

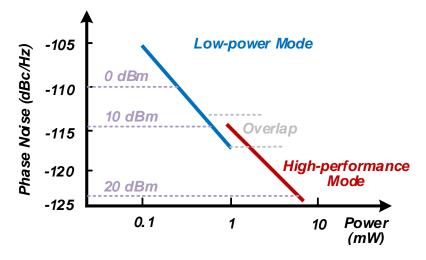

(1.5)